Архитектуры CISC и RISC (часть 4)

4 June 2022, 8:43 pm

Подавляющее число процессоров создано в соответствии с архитектурами CISC и RISC, которые находятся в постоянном развитии. В своей эволюции каждая из них часто заимствует достоинства и решения соперника

Евгений Рудометов

Часть 3

Преимущества и недостатки CISC

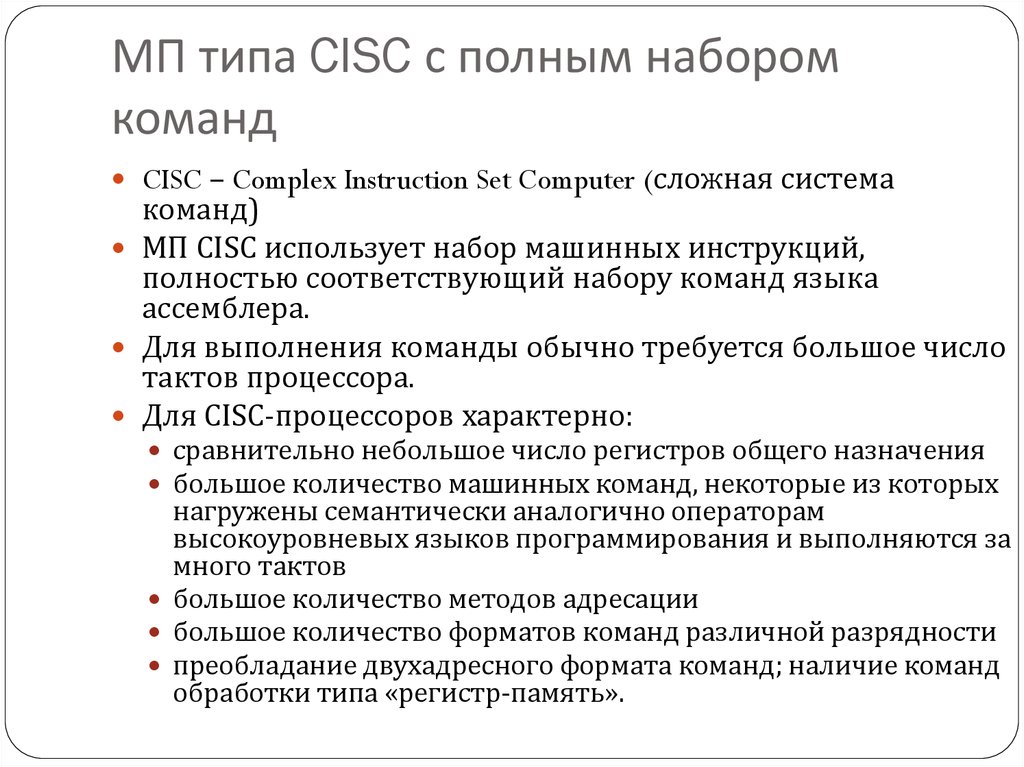

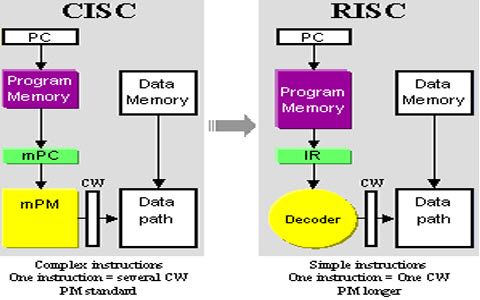

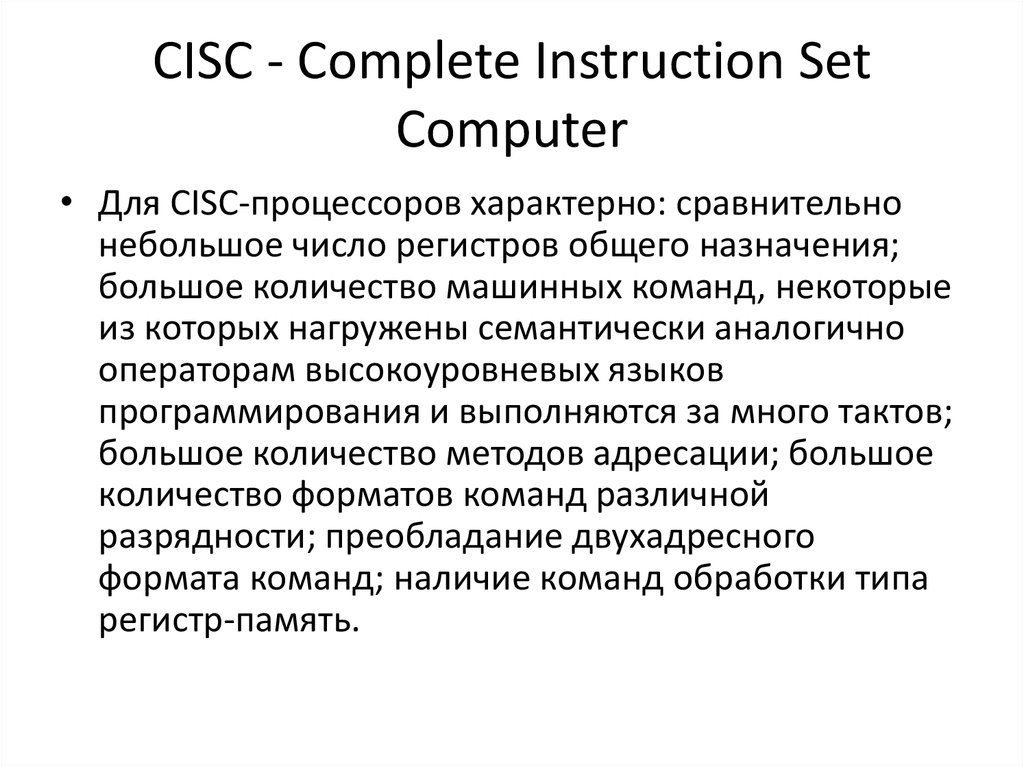

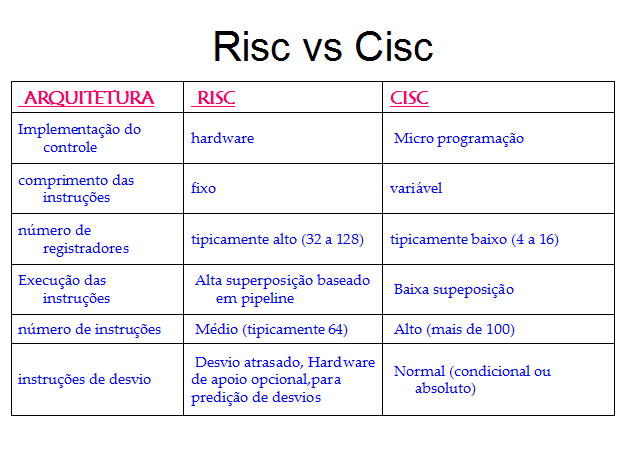

CISC (Complex Instruction Set Computing или Complex Instruction Set Computer) — тип архитектуры процессора с полным набором команд, характеризуется следующими свойствами:

- нефиксированное значение длины команды;

- арифметические действия кодируются в одной команде;

- небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Основоположником CISC-архитектуры многие эксперты считают фирму IBM с архитектурой IBM/360. При этом подходе выполнение любой сколь угодно сложной команды из системы команд процессора реализуется аппаратно средствами процессора. Этот тип архитектуры предусматривает наличие больших наборов команд. Среди этих наборов значительную долю составляют сложные. Их выполнение осуществляется в течение нередко большого числа тактов тактового генератора. Использование сложных команд позволяет решать большое количество задач, упрощает программирование, позволяет сократить размер программ и время их разработки. В качестве примеров процессоров CISC-архитектуры, можно привести большинство процессоров Intel и AMD.

При этом подходе выполнение любой сколь угодно сложной команды из системы команд процессора реализуется аппаратно средствами процессора. Этот тип архитектуры предусматривает наличие больших наборов команд. Среди этих наборов значительную долю составляют сложные. Их выполнение осуществляется в течение нередко большого числа тактов тактового генератора. Использование сложных команд позволяет решать большое количество задач, упрощает программирование, позволяет сократить размер программ и время их разработки. В качестве примеров процессоров CISC-архитектуры, можно привести большинство процессоров Intel и AMD.

Однако этому типу архитектуры присущи и принципиальные недостатки, связанные, прежде всего со сложностью реализации упомянутых функциональных узлов и технологий, а также проблемы с распараллеливанием вычислений сложных команд.

Нельзя сказать, что существующих проблем с архитектурой CISC не видели разработчики процессоров, но их изобретательский потенциал ограничен наличием огромного количества уже разработанного аппаратно-программного обеспечения. Тем не менее, поиски оптимальных путей развития не прекращаются. Одним из альтернативных вариантов является архитектура RISC, разработка которой интенсивно развивается с восьмидесятых годов прошлого столетия, то есть вскоре после появления первых процессоров Intel.

Тем не менее, поиски оптимальных путей развития не прекращаются. Одним из альтернативных вариантов является архитектура RISC, разработка которой интенсивно развивается с восьмидесятых годов прошлого столетия, то есть вскоре после появления первых процессоров Intel.

Эволюция RISC

Преимущества и недостатки RISC

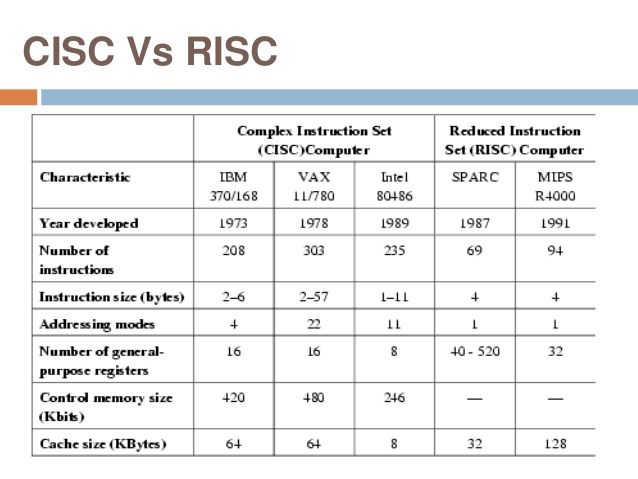

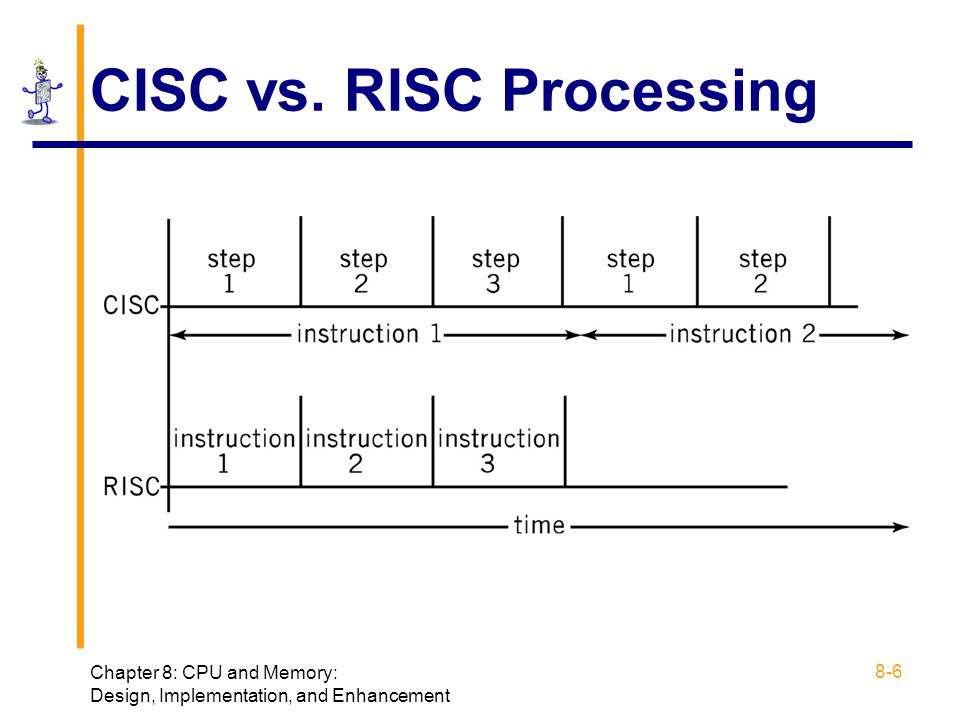

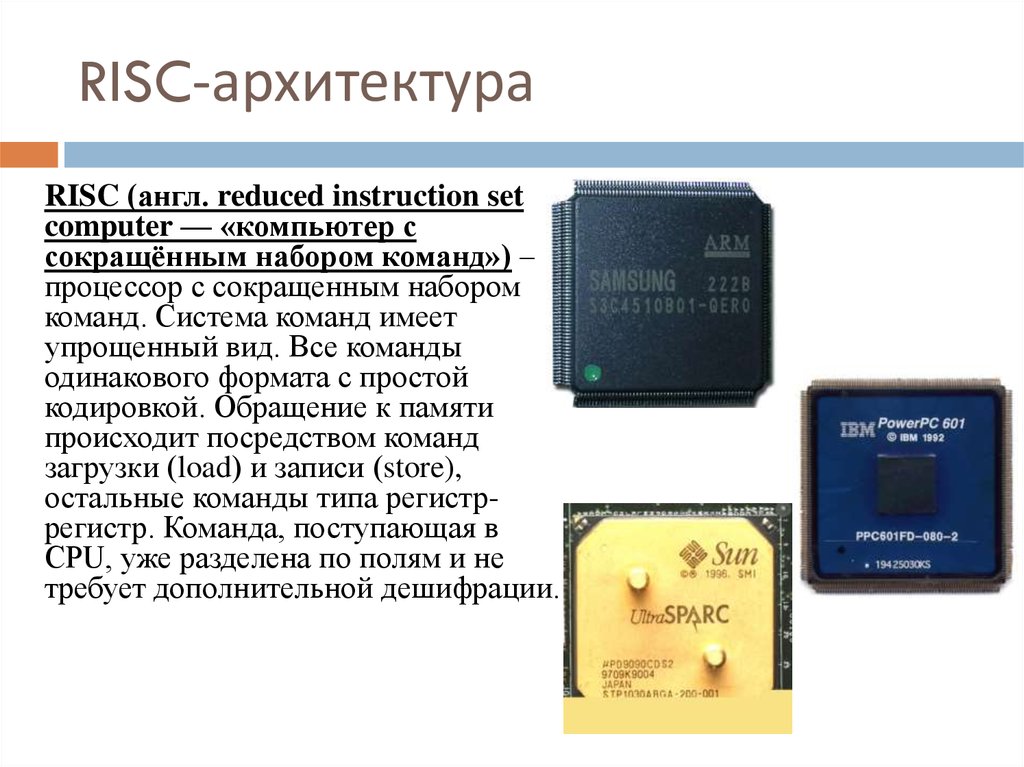

RISC (Restricted (Reduced) Instruction Set Computer — компьютер с сокращенным набором команд) — архитектура процессора, в которой быстродействие увеличивается за счет упрощения инструкций за счет исключения из набора сложных команд, требующих для своего выполнения большого числа тактов. Такой подход делает декодирование простым, а время выполнения — малым. В процессорах с архитектурой RISC применяется ограниченный набор быстрых команд. Согласно идеологии RISC все команды должны выполняться всего за один такт. Это облегчает повышение тактовой частоты и значительно упрощает реализацию суперскалярности (распараллеливание инструкций между несколькими исполнительными блоками). В чипах архитектуры RISC по сравнению с вариантами CISC содержится меньшее количество транзисторов. Это упрощает разработку процессоров, снижает площадь их полупроводниковых кристаллов, уменьшает себестоимость, предоставляет конструкторам возможность снизить уровни энергопотребления и теплообразования.

В чипах архитектуры RISC по сравнению с вариантами CISC содержится меньшее количество транзисторов. Это упрощает разработку процессоров, снижает площадь их полупроводниковых кристаллов, уменьшает себестоимость, предоставляет конструкторам возможность снизить уровни энергопотребления и теплообразования.

Недостатки архитектуры RISC прямо связаны с некоторыми преимуществами этой архитектуры. Так, например, из-за исключения из набора сложных команд выполнение некоторых функций требует использования нескольких простых команд вместо одной сложной. Это удлиняет код программ, требует больших объемов памяти, увеличивает трафик. Исследования показали, что программы в системах RISC в среднем на 30% длиннее программ в системах CISC. Тем не менее, архитектура RISC развивается и находит все больше сторонников среди производителей не только относительно простых контроллеров и встраиваемых систем, но и мобильных, и стационарных компьютерных устройств, и даже серверов. Остается добавить, что идеи RISC нашли воплощение в многочисленных моделях процессоров архитектур MIPS

и ARM.

О MIPS и ARM — в следующей части данной статьи.

>> Часть 5

Ссылки по теме

Filed under All, Все статьи, Процессоры Tagged AMD, ARM, CT, Get, IBM, Intel, IT, NY, PR, Pre, блок, компьютер, контроллер, памяти, поиск, процессор, работа, системы

Comments are closed | Permalink

Виды популярных архитектур процессоров

Прежде чем рассмотреть основные виды архитектур процессоров, необходимо понять, что это такое. Под архитектурой процессора обычно понимают две совершенно разные сущности.

С программной точки зрения архитектура процессора — это совместимость с определённым набором команд (Intel x86), их структуры (система адресации, набор регистров) и способа исполнения (счётчик команд).

Говоря простым языком, это способность программы, собранной для архитектуры x86, работать практически на любой x86-совместимой системе. При этом такая программа не будет работать, например, на ARM системе.

При этом такая программа не будет работать, например, на ARM системе.

С аппаратной точки зрения архитектура процессора — это некий набор свойств и качеств, присущий целому семейству процессоров (Skylake – процессоры Intel Core 5 и 6 поколений).

Если тема кажется сложной, можно начать со статьи о том, чем CPU отличается от GPU.

Виды архитектур

В этой статье мы рассмотрим самые распространенные и актуальные архитектуры с программной точки зрения, кроме узкоспециализированных (графических, математических, тензорных).

CISC

CISC (англ. Complex Instruction Set Computer — «компьютер с полным набором команд») — тип процессорной архитектуры, в первую очередь, с нефиксированной длиной команд, а также с кодированием арифметических действий в одной команде и небольшим числом регистров, многие из которых выполняют строго определенную функцию.

Самый яркий пример CISC архитектуры — это x86 (он же IA-32) и x86_64 (он же AMD64).

В CISC процессорах одна команда может быть заменена ей аналогичной, либо группой команд, выполняющих ту же функцию. Отсюда вытекают плюсы и минусы архитектуры: высокая производительность благодаря тому, что несколько команд могут быть заменены одной аналогичной, но большая цена по сравнению с RISC процессорами из-за более сложной архитектуры, в которой многие команды сложнее раскодировать.

Отсюда вытекают плюсы и минусы архитектуры: высокая производительность благодаря тому, что несколько команд могут быть заменены одной аналогичной, но большая цена по сравнению с RISC процессорами из-за более сложной архитектуры, в которой многие команды сложнее раскодировать.

RISC

RISC (англ. Reduced Instruction Set Computer — «компьютер с сокращённым набором команд») — архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций: их декодирование становится более простым, а время выполнения — меньшим. Первые RISC-процессоры не имели даже инструкций умножения и деления и не поддерживали работу с числами с плавающей запятой.

По сравнению с CISC эта архитектура имеет константную длину команды, а также меньшее количество схожих инструкций, позволяя уменьшить итоговую цену процессора и энергопотребление, что критично для мобильного сегмента. У RISC также большее количество регистров.

Примеры RISC-архитектур: PowerPC, серия архитектур ARM (ARM7, ARM9, ARM11, Cortex).

В общем случае RISC быстрее CISC. Даже если системе RISC приходится выполнять 4 или 5 команд вместо одной, которую выполняет CISC, RISC все равно выигрывает в скорости, так как RISC-команды выполняются в 10 раз быстрее.

Отсюда возникает закономерный вопрос: почему многие всё ещё используют CISC, когда есть RISC? Всё дело в совместимости. x86_64 всё ещё лидер в desktop-сегменте только по историческим причинам. Так как старые программы работают только на x86, то и новые desktop-системы должны быть x86(_64), чтобы все старые программы и игры могли работать на новой машине.

Для Open Source это по большей части не является проблемой, так как пользователь может найти в интернете версию программы под другую архитектуру. Сделать же версию проприетарной программы под другую архитектуру может только владелец исходного кода программы.

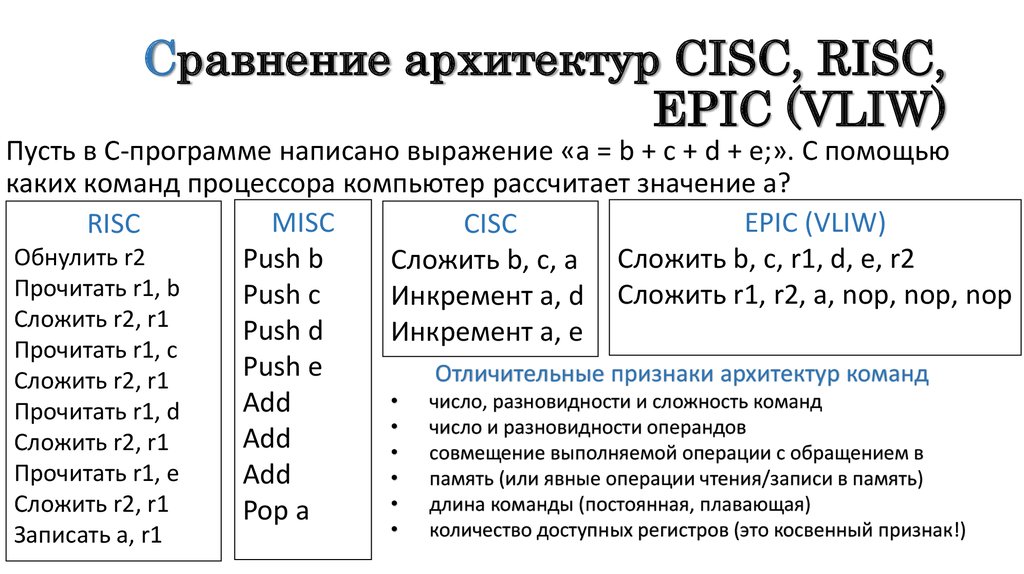

MISC

MISC (англ. Minimal Instruction Set Computer — «компьютер с минимальным набором команд»).

Ещё более простая архитектура, используемая в первую очередь для ещё большего уменьшения итоговой цены и энергопотребления процессора. Используется в IoT-сегменте и недорогих компьютерах, например, роутерах.

Используется в IoT-сегменте и недорогих компьютерах, например, роутерах.

Для увеличения производительности во всех вышеперечисленных архитектурах может использоваться “спекулятивное исполнение команд”. Это выполнение команды до того, как станет известно, понадобится эта команда или нет.

VLIW

VLIW (англ. Very Long Instruction Word — «очень длинная машинная команда») — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно.

По сути является архитектурой CISC со своим аналогом спекулятивного исполнения команд, только сама спекуляция выполняется во время компиляции, а не во время работы программы, из-за чего уязвимости Meltdown и Spectre невозможны для этих процессоров. Компиляторы для процессоров этой архитектуры сильно привязаны к конкретным процессорам. Например, в следующем поколении максимальная длина «очень длинной команды» может из условных 256 бит стать 512 бит, и тут приходится выбирать между увеличением производительности путём компиляции под новый процессор и обратной совместимостью со старым процессором. Опять же, Open Sourсe позволяет простой перекомпиляцией получить программу под конкретный процессор.

Опять же, Open Sourсe позволяет простой перекомпиляцией получить программу под конкретный процессор.

Примеры архитектуры: Intel Itanium, Эльбрус-3.

Виртуальные архитектуры

Но раз нельзя запустить программу одной архитектуры на другой, то откуда берутся магические JAR-файлы, которые можно запустить на любой машине? Это пример виртуальной JVM-архитектуры, которая, по сути, эмулируется на целевой реальной машине. Поэтому достаточно JVM-машины для целевой архитектуры для запуска на ней любой Java-программы. Другим примером виртуальной архитектуры является .NET CIL.

Из минусов виртуальных архитектур можно выделить меньшую производительность по сравнению с реальными архитектурами. Этот минус нивелируется с помощью JIT- и AOT-компиляции. Однако большим плюсом будет кроссплатформенность.

Дальнейшим развитием этих архитектур стали гибридные архитектуры. Например современные x86_64 процессоры хотя и CISC-совместимы, но являются процессорами с RISC-ядром. В таких гибридных CISC-процессорах CISC-инструкции преобразовываются в набор внутренних RISC-команд. Какое дальнейшее развитие получат архитектуры процессора, покажет только время.

Какое дальнейшее развитие получат архитектуры процессора, покажет только время.

Иван Борисов

Что такое процессор CISC? Особенности, архитектура, преимущества, недостатки и области применения процессора CISC

CISC означает C комплекс I инструкция S и C компьютер. Процессор CISC — это классификация микропроцессорной конструкции ЦП, которая работает с большими и сложными наборами инструкций, чтобы выполнять различные задачи с использованием минимально возможных кодов. Он основан на подходе к выполнению более чем одной инструкции за цикл.

Проще говоря, дизайн процессора CISC основан на подходе к завершению всей операции в нескольких строках кода на языке ассемблера.

Содержание: Процессор CISC

- Введение

- Характеристики

- Архитектура

- RISC-подход

- Преимущества

- Недостатки

- Приложения

Введение в CISC

Ранее мы обсуждали RISC-процессор, т. е. компьютерный процессор с сокращенным набором команд, который использует совершенно иной подход к работе, чем CISC-процессор. Процессор RISC использует подход увеличения внутреннего параллелизма за счет выполнения простого набора инструкций за один такт. Однако процессоры CISC вместо использования различных простых инструкций используют сложные наборы инструкций для выполнения любой поставленной задачи.

е. компьютерный процессор с сокращенным набором команд, который использует совершенно иной подход к работе, чем CISC-процессор. Процессор RISC использует подход увеличения внутреннего параллелизма за счет выполнения простого набора инструкций за один такт. Однако процессоры CISC вместо использования различных простых инструкций используют сложные наборы инструкций для выполнения любой поставленной задачи.

CISC был введен в 1970 году и обрабатывает выполнение инструкций без использования нескольких кодов. Он основан на сложной природе архитектуры набора команд.

Основной целью разработки CISC является создание такого набора инструкций, который хорошо работает с задачами и структурами данных языков высокого уровня. Эта архитектура поддерживает множество режимов адресации и, следовательно, длина инструкции носит переменный характер. Это означает, что в данном случае весь упор делается на аппаратную часть системы. Процессоры CISC тщательно разработаны для обеспечения прямой аппаратной поддержки разработчика.

Нам известно, что микропроцессоры — это процессоры данных, которые собирают информацию, выполняют необходимые модификации в соответствии с предопределенными наборами инструкций, а результаты сохраняются и используются в случае дальнейших операций внутри систем. Мы знаем, что любая операция выполняется в наборе путей, включающих выборку, декодирование и выполнение.

В CISC работа компилятора несколько сокращается, так как максимальный упор делается на генерацию машинных инструкций для процессора, где одна инструкция может выполнять такие задачи, как загрузка, оценка, сохранение и т. д., таким образом, считается сложной по своей природе. Однако это уменьшает работу компилятора по написанию длинных машинных инструкций для любого рода операций. Он включает в себя микропрограммируемый блок управления.

Функции процессора CISC

Процессор CISC обладает следующими функциями:

- Декодирование : Инструкции имеют сложный характер, поэтому предлагается сложное декодирование инструкций.

- Размер инструкции : Инструкции в этом процессоре имеют большой размер и переменный характер.

- Типы данных и режимы адресации : включает больше типов данных и сложные режимы адресации.

- Регистры общего назначения : Операции выполняются в самой памяти, а результаты операций также сохраняются в памяти, поэтому по этой причине в случае процессоров CISC требуется меньше регистров общего назначения.

- Тактовый цикл : Поскольку размер инструкций здесь является переменным, для выполнения инструкции может использоваться более одного такта.

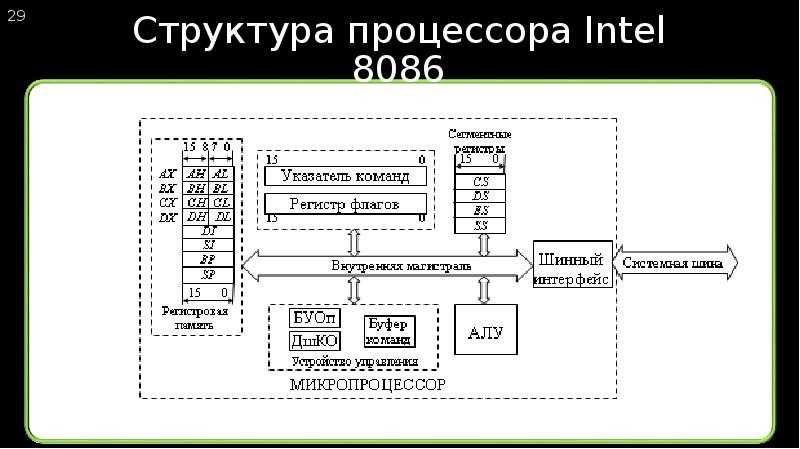

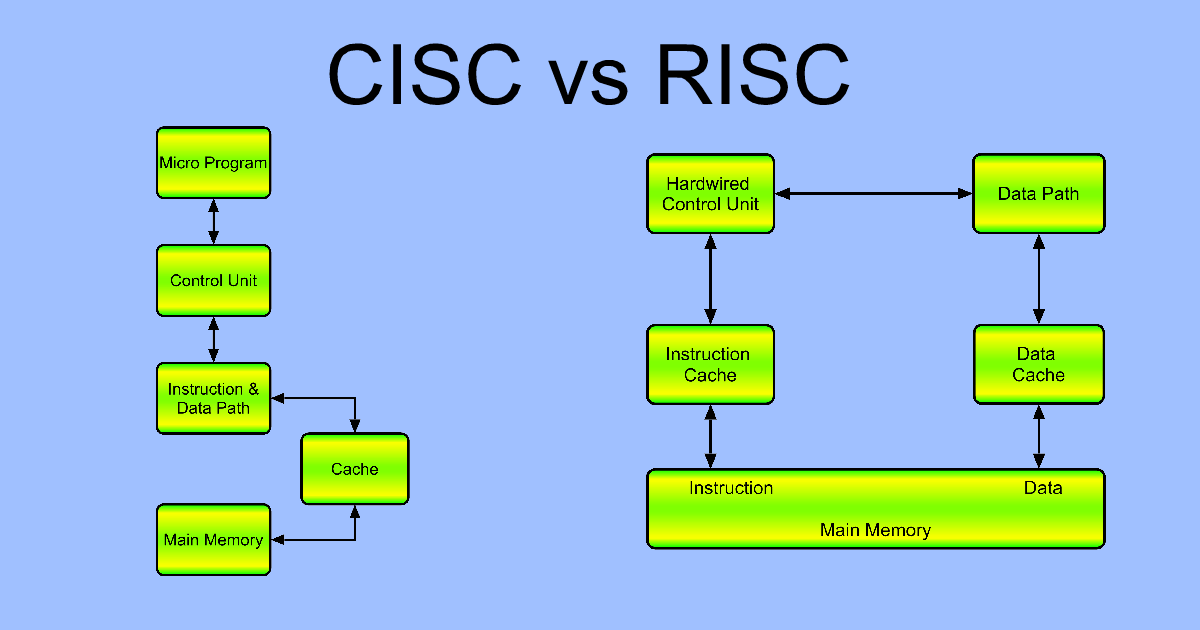

Архитектура процессора CISC

Из приведенного выше обсуждения следует, что процессоры CISC спроектированы таким образом, что для выполнения одной и той же операции требуется меньше инструкций по сравнению с процессорами RISC.

Рисунок ниже представляет архитектурное представление процессора CISC:

В общем, любой процессор работает таким образом, что ПК хранит 16-битный адрес инструкции, которая должна быть выбрана. На следующем этапе инструкция по соответствующему адресу извлекается из памяти и загружается в шину данных, а затем направляется к блоку декодирования. Как только декодер инструкций получает инструкцию, он проверяет код операции, который должен быть выполнен, и операнд, над которым должна быть выполнена операция. Однако тем временем должны быть получены следующие данные, которые требует код операции, и поэтому для них блок управления генерирует необходимый управляющий сигнал.

На следующем этапе инструкция по соответствующему адресу извлекается из памяти и загружается в шину данных, а затем направляется к блоку декодирования. Как только декодер инструкций получает инструкцию, он проверяет код операции, который должен быть выполнен, и операнд, над которым должна быть выполнена операция. Однако тем временем должны быть получены следующие данные, которые требует код операции, и поэтому для них блок управления генерирует необходимый управляющий сигнал.

В ходе текущей операции ПК увеличивается на 1, чтобы представить адрес памяти следующего местоположения, откуда требуется выборка. И как только ПК удерживает новое значение, это значение загружается в адресную защелку, чтобы заново начать новый цикл памяти. Кроме того, как и в предыдущем сценарии, 16-битный адрес размещается на адресной шине, которая передается декодеру команд, который помогает загрузить его в память. Произойдет необходимая операция и результат операции сохранится в памяти.

Таким образом, рабочий процесс процессора поддерживается последовательными повторяющимися циклами.

Эта архитектура CISC предлагает сложное декодирование инструкций, поскольку для одной инструкции требуется несколько режимов адресации. Однако, поскольку операции происходят в самой памяти, требуется не так много регистров общего назначения.

Подход CISC

Ранее мы обсуждали подход RISC, в котором работа компилятора заключается в упрощении сложной инструкции до нескольких простых инструкций, которые могут выполняться конвейерным образом, чтобы выполнять желаемую операцию с большей скоростью. Однако в этом случае работа компилятора по упрощению инструкций значительно сокращается, поскольку аппаратное обеспечение рассчитано даже на выполнение сложных инструкций.

Архитектура CISC позволяет процессору выполнять задачу с наименьшим количеством возможных кодов языка ассемблера.

В подходе RISC мы обсуждали, что для выполнения сложных инструкций процессор выполняет различные команды, которые в результате выполняют желаемую операцию.

Предположим, что MUL представляет собой сложную инструкцию, результатом которой является произведение двух значений. В случае RISC данные, над которыми должна быть выполнена операция, имеющиеся в памяти, сначала загружаются в регистр с помощью отдельных инструкций. Затем используется соответствующая команда для выполнения требуемой операции над данными в регистрах. Наконец, результат операции загружается обратно в память.

В случае RISC данные, над которыми должна быть выполнена операция, имеющиеся в памяти, сначала загружаются в регистр с помощью отдельных инструкций. Затем используется соответствующая команда для выполнения требуемой операции над данными в регистрах. Наконец, результат операции загружается обратно в память.

Подход CISC сильно отличается от RISC. В отличие от RISC, в случае CISC нет необходимости загружать данные из памяти в регистр для выполнения операции. Здесь просто данные в памяти напрямую используются для выполнения желаемой операции. Предположим, если мы рассмотрим схему хранения компьютерной системы, которая представляет, что данные, над которыми должна быть выполнена операция, находятся в ячейках памяти 2:1 и 3:5.

Здесь в этой инструкции не нужны отдельные команды загрузки или сохранения, достаточно одной инструкции:

MUL 2:1, 3:5

Результат операции сохраняется в одной из ячеек памяти.

Допустим, x = 2:1 и y = 3:5, тогда команда MUL 2:1, 3:5 эквивалентна

x = x . y

y

Преимущества

- Размеры кода малы в случае процессоров CISC.

- Работа компилятора в значительной степени сокращается, оператор языка высокого уровня не требуется преобразовывать в язык ассемблера.

- Длина шорткода поддерживает меньшие требования к оперативной памяти.

Недостатки

- Высокая сложность делает систему несколько неэффективной.

- Инструкция выполняется более чем за один такт.

- Не поддерживает конвейерную обработку инструкций.

Приложения

Процессоры CISC в основном связаны с приложениями реального времени, такими как системы безопасности, домашняя автоматизация и т. д.

Что такое процессоры CISC? Архитектура, примеры, набор инструкций, преимущества и недостатки

CISC является аббревиатурой от Complex Instruction Set Computer . Процессоры CISC были разработаны в 1970-х годах до появления процессоров RISC (компьютеры с сокращенным набором инструкций). В этот период память компьютера «маленькая» и «очень дорогая».

В этот период память компьютера «маленькая» и «очень дорогая».

Процессоры CISC помогли упростить код и сделать его на короче , чтобы уменьшить потребность в памяти. В процессоре CISC одна инструкция имеет «несколько низкоуровневых операций». Это делает инструкции CISC короткими, но «сложными».

В этом разделе мы узнаем об архитектуре, наборе инструкций, конвейерной обработке в процессорах CISC, их преимуществах и недостатках. Итак, начнем с темы.

Содержание: Процессоры CISC

- Архитектура CISC

- Набор инструкций CISC

- Конвейерная обработка в процессоре CISC

- Преимущества и недостатки

- Ключевые выводы

Архитектура процессоров CISC

Как мы узнали выше, основная цель процессора CISC — минимизировать размер программы на уменьшить количество инструкций в программе. Это делается путем «встраивания некоторых низкоуровневых инструкций в одну сложную инструкцию». Позже при декодировании эта инструкция генерирует несколько микроинструкций для выполнения.

Позже при декодировании эта инструкция генерирует несколько микроинструкций для выполнения.

Теперь, если программа/программное обеспечение упрощается, то аппаратное обеспечение должно работать и выполнять сложные задачи. Вот почему процессор CISC имеет сложное аппаратное обеспечение. Блок-схема архитектуры CISC приведена ниже:

Здесь у вас есть специальный блок управления микропрограммой , который использует серию микроинструкций микропрограммы, хранящихся в «памяти управления» блока управления микропрограммой , и генерирует управляющие сигналы .

Блоки управления получают доступ к управляющим сигналам , вырабатываемым блоком управления микропрограммой , и управляют работой аппаратных средств процессоров.

Путь инструкций и данных извлекает код операции и операнды инструкций из памяти.

Кэш и основная память — это место, где хранятся программные инструкции и операнды.

Примеры процессоров CISC:

IBM 370/168, VAX 11/780, Intel 80486.

Наборы инструкций для процессоров CISC

Память. Подобно тому, как RISC использует Load/Store для доступа к операндам памяти, CISC имеет Переместить инструкцию для доступа к операндам памяти.Но, в отличие от Load and Store, операция Move в CISC имеет более широкий охват. Инструкции CISC могут «напрямую обращаться к операндам памяти».

Общий формат инструкции Move:

Move назначение, источник

Она может переместить непосредственный операнд в ячейку памяти или в регистр .

Ход А, 100

Move R, 100

Он может передавать операнд между двумя ячейками памяти .

Переместить A, B

Он может передавать операнд между двумя регистрами .

Переместить R1, R2

Включая пять основных режимов адресации, таких как:

Немедленный режим, прямой/абсолютный режим, режим регистрации, косвенный режим и индексный режим.

Набор инструкций CISC имеет несколько дополнительных режимов адресации. Это «режим автоматического увеличения», «режим автоматического уменьшения» и «относительный режим».

Режим автоинкремента :

Здесь эффективным адресом операнда является содержимое регистра. После доступа к содержимому регистра оно автоматически увеличивается, чтобы указать место в памяти следующего операнда.

Режим автодекремента:

Здесь также эффективным адресом операнда является содержимое регистра. Но здесь сначала содержимое регистра уменьшается, а затем содержимое регистра используется как эффективный адрес для операнда.

Относительный режим:

Он аналогичен «Режиму индексного регистра», где эффективный адрес получается путем добавления константы к содержимому регистра общего назначения. В относительном режиме вместо регистра общего назначения используется программный счетчик . Этот вид режима адресации используется для обращения к большому диапазону областей памяти.

В относительном режиме вместо регистра общего назначения используется программный счетчик . Этот вид режима адресации используется для обращения к большому диапазону областей памяти.

Выше мы упомянули, что процессор CISC сводит к минимуму количество инструкций, что делает код относительно короче.

Давайте посмотрим, как инструкции стиля CISC минимизируют длину кода?

Предположим, у нас есть операция

A = B+C

RISC Набор инструкций для этого будет:

Нагрузка R2, B

Нагрузка R3, C

9993 ADD RO4. , R2, R3Store R4, A

Теперь давайте посмотрим на набор инструкций CISC для той же операции.

Перемещение А, В

Добавить A, C

Цель четырех инструкций стиля RISC достигается только двумя инструкциями стиля CISC.

Таким образом, можно сказать, что архитектура CISC эффективно минимизирует количество инструкций в программе, так как выполнение одной инструкции выполняет несколько низкоуровневых инструкций в программе.

Конвейерная обработка в процессорах CISC

Инструкции в стиле RISC упрощают реализацию конвейерной обработки, поскольку все они состоят из одно слово . Операнды всех инструкций находятся в одном и том же месте в слове. За исключением инструкций Load и Store , все остальные инструкции работают с операндами регистра .

Таким образом становится легко реализовать конвейерную обработку инструкций в стиле RISC. Но это не относится к инструкциям в стиле CISC. Инструкции CISC имеют «переменную длину», они имеют «несколько операндов», «сложные режимы адресации» и «сложные инструкции».

Теперь инструкция CISC занимает на больше, чем слово памяти . Таким образом, потребуется несколько циклов для выборки операнда. Кроме того, мы знаем, что инструкции имеют переменный размер и формат, что усложняет декодирование инструкций и выборку операндов. Вот почему реализация конвейерной обработки инструкций в стиле CISC является сложной задачей.

Таким образом, потребуется несколько циклов для выборки операнда. Кроме того, мы знаем, что инструкции имеют переменный размер и формат, что усложняет декодирование инструкций и выборку операндов. Вот почему реализация конвейерной обработки инструкций в стиле CISC является сложной задачей.

Разберем это на примере:

Переместить (R2), (R3)

Переместить (R4), R5

В первой инструкции Move эффективных адреса s обоих операндов являются ячейкой памяти . Таким образом, потребуется два доступа к памяти.

Во второй инструкции перемещения эффективный адрес «первого операнда» является ячейкой памяти , а эффективный адрес «второго операнда» является регистром . Второй инструкции требуется только один доступ к памяти. Здесь вторая инструкция Move должна быть останавливает так, что первая инструкция Move может завершить доступ к обоим операндам из памяти.

Следовательно, реализация конвейерной обработки инструкций в стиле CISC довольно сложна.

Преимущества и недостатки процессоров CISC

Преимущества:

- Размер кода сравнительно на короче , что минимизирует требования к памяти.

- Выполнение одной инструкции выполняет несколько низкоуровневых задач .

- Комплексный режим адресации делает доступ к памяти гибким .

- Инструкция CISC может напрямую обращаться к ячейкам памяти .

Недостатки:

- Хотя размер кода сведен к минимуму, но для выполнения одной инструкции требуется несколько тактов . Таким образом, снижается общая производительность компьютера.

- Реализация конвейерная обработка для инструкции CISC немного сложна .