физические, виртуальные, логические, линейные, эффективные, гостевые / Хабр

Мне периодически приходится объяснять разным людям некоторые аспекты архитектуры Intel® IA-32, в том числе замысловатость системы адресации данных в памяти, которая, похоже, реализовала почти все когда-то придуманные идеи. Я решил оформить развёрнутый ответ в этой статье. Надеюсь, что он будет полезен ещё кому-нибудь.

При исполнении машинных инструкций считываются и записываются данные, которые могут находиться в нескольких местах: в регистрах самого процессора, в виде констант, закодированных в инструкции, а также в оперативной памяти. Если данные находятся в памяти, то их положение определяется некоторым числом — адресом. По ряду причин, которые, я надеюсь, станут понятными в процессе чтения этой статьи, исходный адрес, закодированный в инструкции, проходит через несколько преобразований.

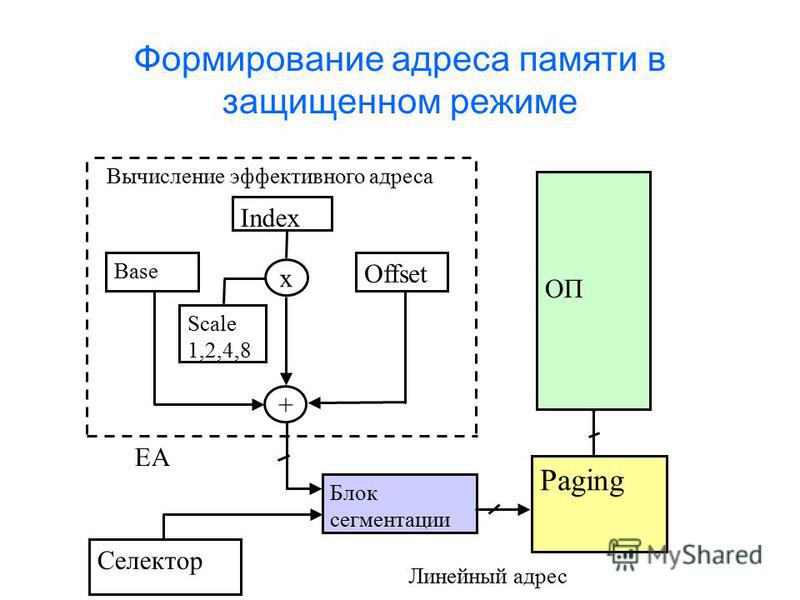

На рисунке — сегментация и страничное преобразование адреса, как они выглядели 27 лет назад. Иллюстрация из Intel 80386 Programmers’s Reference Manual 1986 года. Забавно, что в описании рисунка есть аж две опечатки: «803

Иллюстрация из Intel 80386 Programmers’s Reference Manual 1986 года. Забавно, что в описании рисунка есть аж две опечатки: «803

Начнём немного с конца — с цели всей цепочки преобразований.

Физический адрес

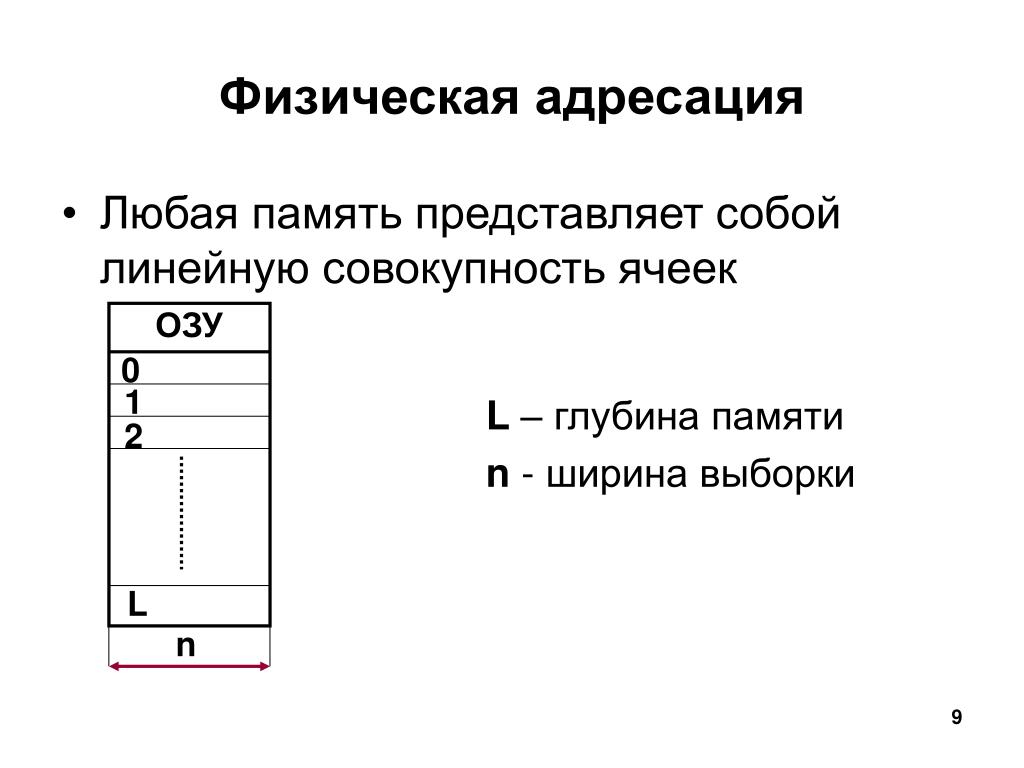

Конечный результат всех преобразований других типов адресов, перечисленных далее в этой статье — физический адрес. На нём кончается работа внутри центрального процессора по преобразованию адресов.

Конечный результат?!

На самом деле, легко понять, что это ещё не конец. В платформе, которая должна обработать запрос данных от процессора, может быть несколько чипов DRAM, имеющих собственную структуру разбиения на блоки, а также различные периферийные устройства, отображённые на общее пространство физической памяти. Дальнейший путь транзакции с некоторым физическим адресом будет зависеть от конфигурации нескольких декодеров, находящихся на её пути внутри устройств платформы.

Эффективный адрес

Эффективный адрес — это начало пути. Он задаётся в аргументах индивидуальной машинной инструкции, и вычисляется из значений регистров, смещений и масштабирующих коэффициентов, заданных в ней явно или неявно.

Например, для инструкции (ассемблер в AT&T-нотации)

addl %eax, 0x11(%ebp, %edx, 8)

эффективный адрес операнда-назначения будет вычислен по формуле:

eff_addr = EBP + EDX * 8 + 0x11

Логический адрес

Без знания номера и параметров сегмента, в котором указан эффективный адрес, последний бесполезен. Сам сегмент выбирается ещё одним числом, именуемым селектором. Пара чисел, записываемая как selector:offset, получила имя логический адрес. Так как активные селекторы хранятся в группе специальных регистров, чаще всего вместо первого числа в паре записывается имя регистра, например, ds:0x11223344.

Здесь обычно у тех, кто столкнулся с этими понятиями впервые, голова начинает идти кругом. Несколько упростить (или усложнить) ситуацию помогает тот факт, что почти всегда выбор селектора (и связанного с ним сегмента) делается исходя из «смысла» доступа. По умолчанию, если в кодировке машинной инструкции не сказано иного, для получения адресов кода используются логические адреса с селектором CS, для данных — с DS, для стека — с SS.

Линейный адрес

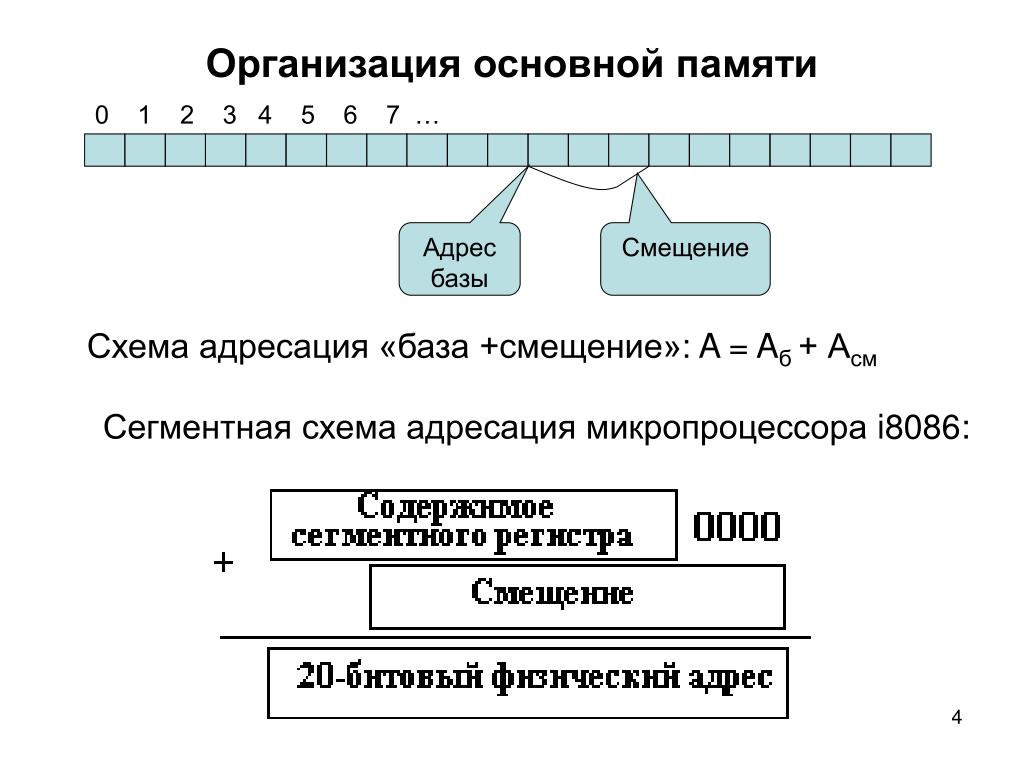

Эффективный адрес — это смещение от начала сегмента — его базы. Если сложить базу и эффективный адрес, то получим число, называемое линейным адресом:

lin_addr = segment.base + eff_addr

Преобразование логический → линейный не всегда может быть успешным, так как при его исполнении проверяется несколько условий на свойства сегмента, записанных в полях его дескриптора. Например, проверяется выход за границы сегмента и права доступа.

Реальный режим

Описанное выше верно при включенной сегментации.

Сегментация была модной на некотором этапе развития вычислительной техники. В настоящее она почти всюду была заменена другими механизмами, и используется только для специфических задач. Так, в режиме IA-32e (64-битном) только два сегмента могут иметь ненулевую базу. Для остальных четырёх в этом режиме всегда линейный адрес == эффективный.

Что такое виртуальный адрес?

В литературе и в документации других архитектур встречается ещё один термин — виртуальный адрес. Он не используется в документации Intel на IA-32, однако встречается, например, в описании Intel® Itanium, в котором сегментация не используется. Можно смело считать, что для IA-32 виртуальный == линейный.

В советской литературе по вычислительной технике этот вид адресов также именовался математическим.

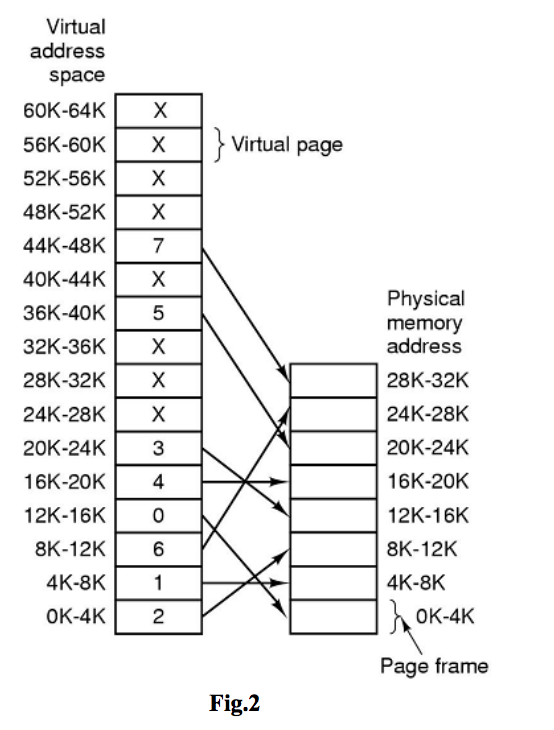

Страничное преобразование

Следующее после сегментации преобразование адресов: линейный → физический — имеет множество вариаций в своём алгоритме, в зависимости от того, в каком режиме (32-битном, PAE или 64-битном) находится процессор.

Что влияет на paging

Примечательно, сколько различных бит из разных системных регистров процессора влияют на процесс страничного преобразования в настоящее время. Я просмотрел свежую сентябрьскую редакцию Intel SDM [1], и вот полный список: CR0.WP, CR0.PG, CR4.PSE, CR4.PAE, CR4.PGE, CR4.PCIDE, CR4.SMEP, CR4.SMAP, IA32_EFER.LME, IA32_EFER.NXE, EFLAGS.AC.

Однако общая идея всегда одна и та же: линейный адрес разбивается на несколько частей, каждая из которых служит индексом в одной из системных таблиц, хранящихся в памяти.

В разных режимах процессора различается число и ёмкость этих таблиц. Преобразование может завершиться неудачей, если очередная таблица не содержит валидных данных, или права доступа, хранящиеся в последней из них, запрещают доступ к странице; например, при записи в регионы, помеченные как «только для чтения», или попытке чтения памяти ядра из непривилегированного процесса.

Гостевой физический

До введения возможностей аппаратной виртуализации в процессорах Intel страничное преобразование было последним в цепочке. Когда же на одной системе работают несколько виртуальных машин, то физические адреса, получаемые в каждой из них, приходится транслировать ещё один раз.

Полная картина

Я попытался собрать все преобразования адреса в одну иллюстрацию. В ней преобразования обозначены стрелками, типы адресов обведены в рамки.

Как уже было сказано выше, каждое из преобразований может вернуть ошибку для адресов, не имеющих представления в следующем по цепочке виде. Устранение подобных проблем — это задача операционных систем и мониторов виртуальных машин, реализующих абстракцию виртуальной памяти.

Заключение

Эволюция, что в природе, что в технике — странная вещь. Она порождает неожиданные структуры, необъяснимые с точки зрения рационального проектирования. Её творения полны атавизмов, правила их поведения иногда почти полностью состоят из исключений. Для того, чтобы понять работу такой системы, часто требуется прокрутить её эволюцию с самого начала, и под нагромождениями всех слоёв найти истину в виде принципа: «ничего не выбрасывать». Я склонен считать архитектуру IA-32 замечательным примером эволюционного развития.

P.S. Всё как у всех

Вскоре после завершения написания этой статьи я натолкнулся на презентацию об архитектуре IBM System z, которая примечательна в том числе своей долгой и интересной историей поддержки виртуализации. В этом документе нашлось перечисление всех типов адресов памяти, используемых в System z:

- Virtual: Translated by dynamic address translation (DAT) to real addresses

- Real: Translated to absolute addresses using the prefix register

- Absolute: After applying the prefix register

- Logical: The address seen by the program (this can either be a virtual or a real address)

- Physical: translated to absolute addresses by the Config Array

Как можно заметить, их тоже пять.

Спасибо за внимание!

Литература

- Intel Corporation. Intel® 64 and IA-32 Architectures Software Developer’s Manual. Volumes 1–3, 2014. www.intel.com/content/www/us/en/processors/architectures-software-developer-manuals.html

Адресация памяти | это… Что такое Адресация памяти?

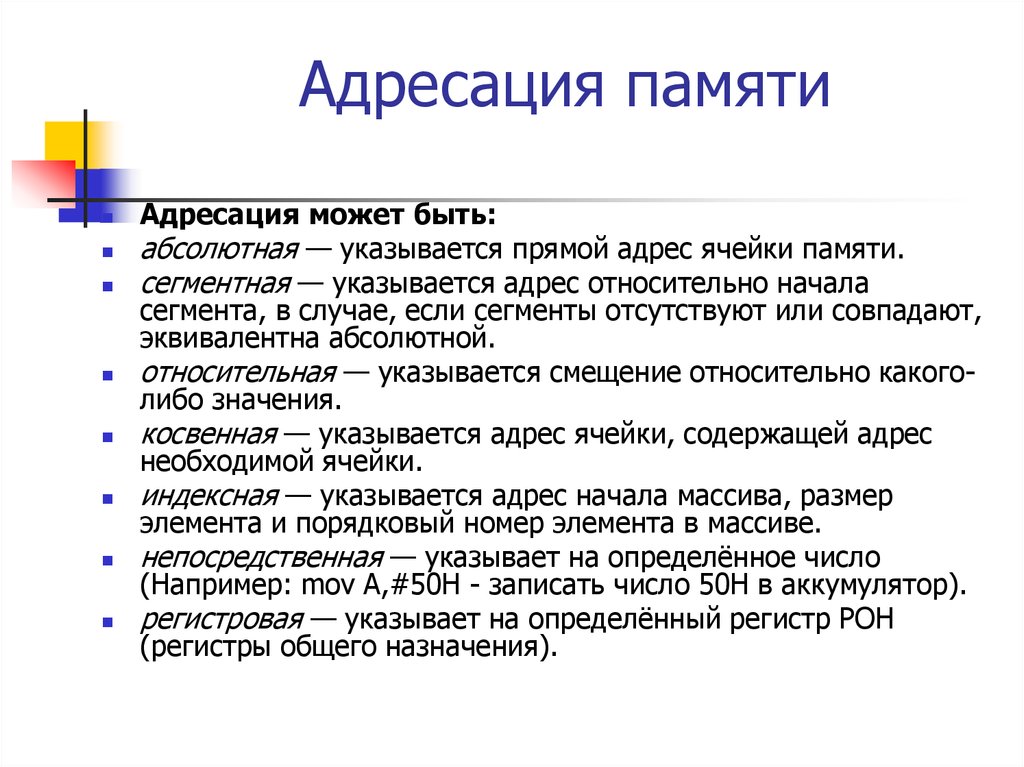

Адресация — осуществление ссылки (обращение) к устройству или элементу данных по его адресу[1]; установление соответствия между множеством однотипных объектов и множеством их адресов; метод идентификации местоположения объекта[2].

Содержание

|

Методы адресации

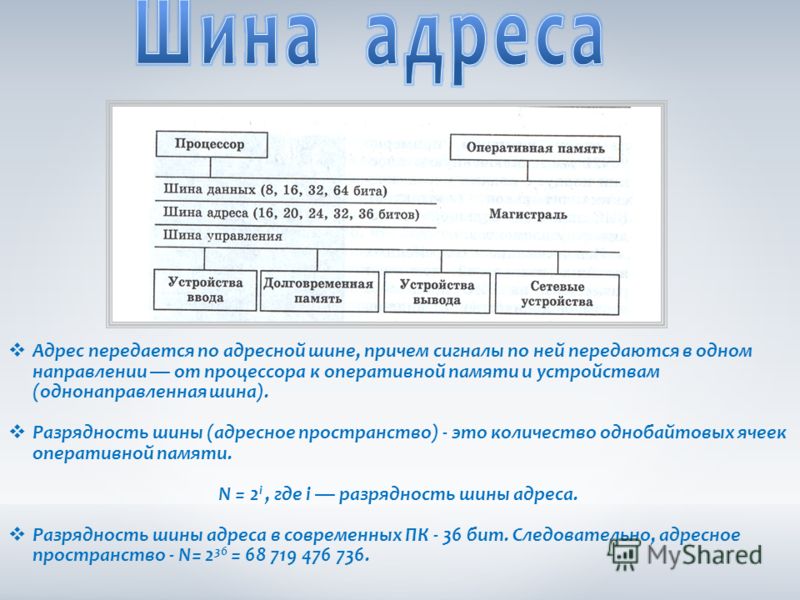

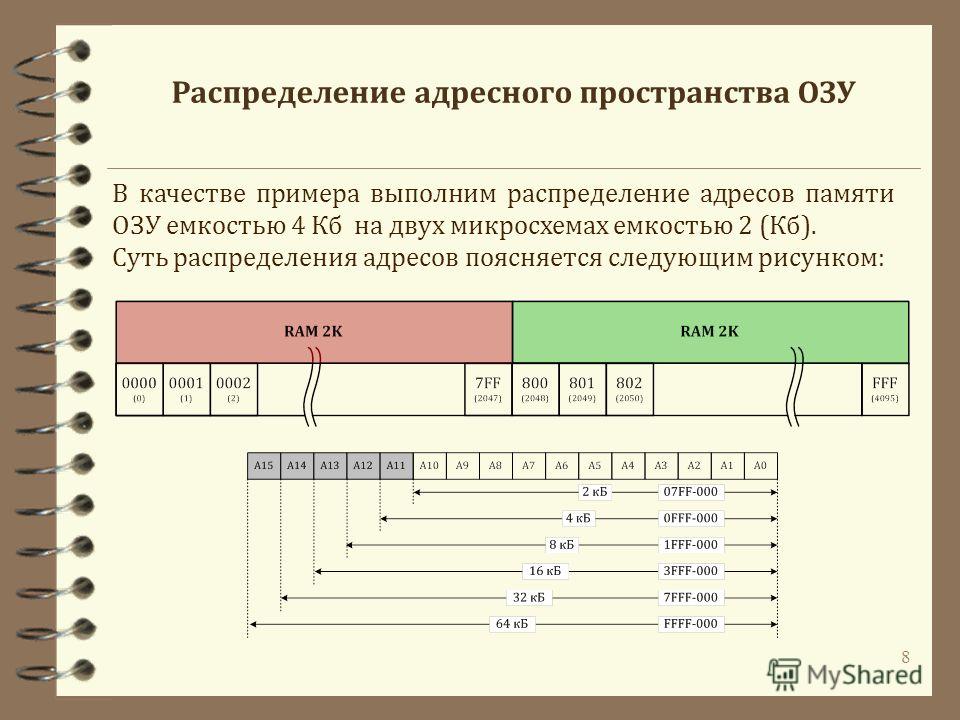

[2]Адресное пространство

- Простая (англ. flat addressing) — указание объекта с помощью идентификатора или числа, не имеющего внутренней структуры.

- Расширенная (англ. extended addressing) — доступ к запоминающему устройству с адресным пространством, бо́льшим диапазона адресов, предусмотренного форматом команды.

- Виртуальная (англ. virtual addressing) — принцип, при котором каждая программа рассматривается как ограниченное непрерывное поле логической памяти, а адреса этого поля — как виртуальные адреса.

- Ассоциативная (англ. associative addressing) — точное местоположение данных не указывается, а задаётся значение определённого поля данных, идентифицирующее эти данные (см.: Ассоциативная память).

Исполнение программ

- Статическая (англ. static addressing) — соответствие между виртуальными и физическими адресами устанавливается до начала и не меняется в ходе выполнения программы.

- Динамическая (англ. dynamic addressing) — преобразование виртуальных адресов в физические осуществляется в процессе выполнения программы. Программа при этом не зависит от места размещения в физической памяти и может перемещаться в ней в процессе выполнения.

Кодирование адресов

- Явная (англ. explicit addressing) — адресация путём явного задания адресов в программе.

- Неявная (англ. implied addressing) — один или несколько операндов или адресов операндов находятся в фиксированных для данной команды регистрах или ячейках памяти и не требуют явного указания в команде.

- Абсолютная (англ. absolute addressing) — адресная часть команды содержит абсолютный адрес.

- Символическая (англ. symbolic addressing) — адресная часть команды содержит символический адрес.

Вычисление адресов

- Непосредственная, прямая (англ. immediate (direct) addressing) — адресная часть команды содержит непосредственный (прямой) адрес; адресация путём указания прямых адресов.

- Косвенная (англ. indirect addressing) — адресная часть команды содержит косвенный адрес; адресация посредством косвенных адресов.

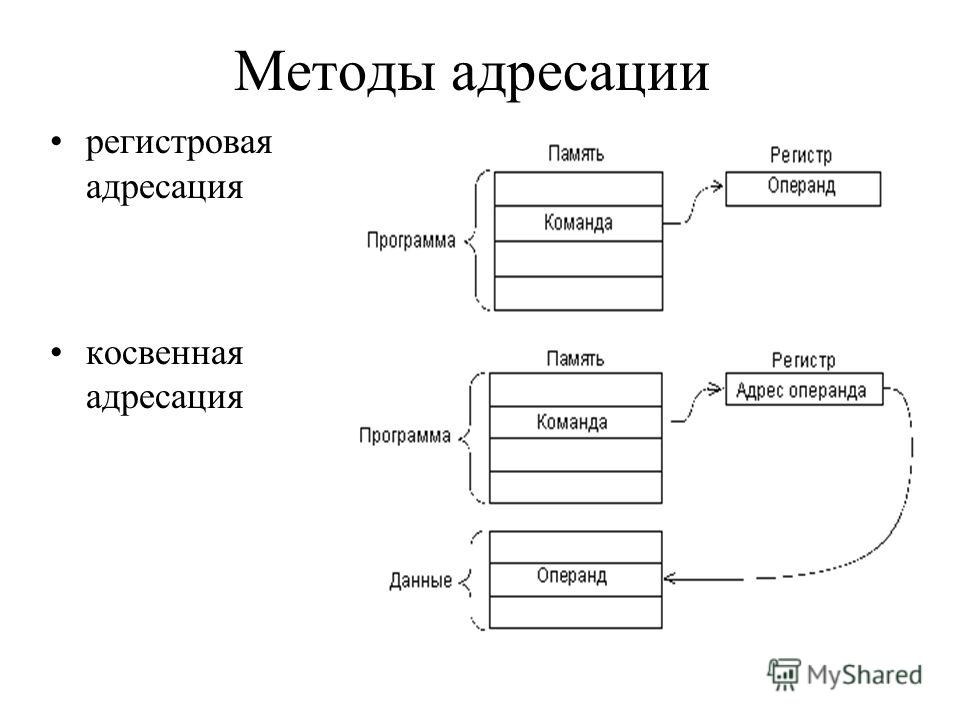

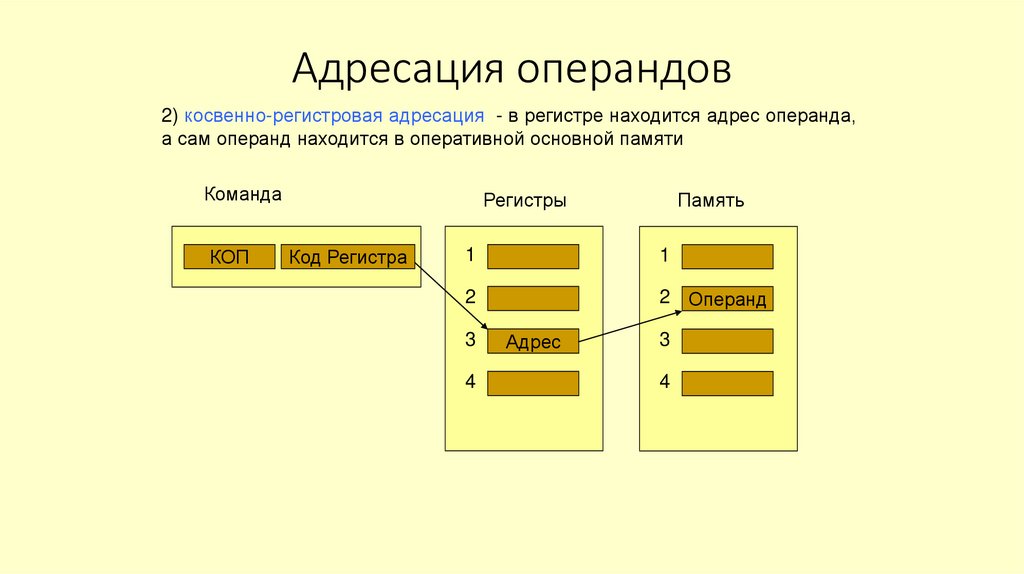

- Регистровая (англ. register addressing) — задание адресов операндов в регистрах.

- Базисная (англ. basic addressing) — вычисление адресов в машинных командах относительно содержимого регистра, указанного в качестве базового.

- Базовая (англ. base-displacement addressing) — схема вычисления исполнительного адреса, при которой этот адрес является суммой базового адреса и смещения.

- Относительная (англ. relative addressing) — адресная часть команды содержит относительный адрес.

- Индексная (англ. indexed addressing) — формирование исполнительного адреса осуществляется путём добавления к базовому адресу содержимого индексного регистра.

- Автодекрементная, автоинкрементная (англ. autodecremental, autoincremental addressing — содержимое регистра индекса изменяется (уменьшается или увеличивается) на некоторое число.

- Постдекрементная, предекрементная, постинкрементная, преинкрементная — автодекрементные и автоинкрементные адресации, при которых уменьшение/увеличение происходит после/до выборки операнда.

- Стековая (англ. stack addressing) — адресация посредством регистра — указателя стека.

- Самоопределяющаяся (англ. self-relative addressing) — адресная часть команды содержит самоопределяющийся адрес.

- Адресация относительно счётчика команд (англ. program counter relative addressing) — адреса в команде указываются в виде разности исполнительных адресов и адреса исполняемой команды. Такой способ адресации не требует настройки (см. также: Позиционно-независимый код).

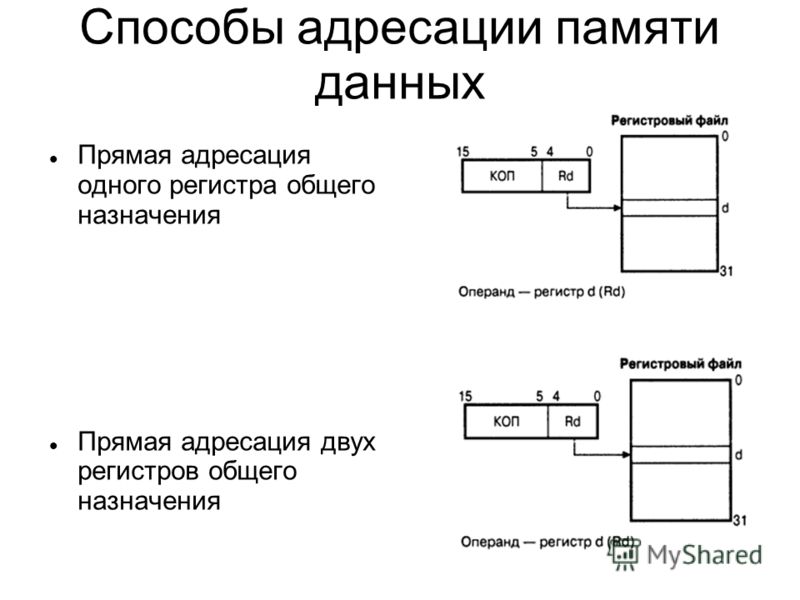

Способы адресации

Подразумеваемый операнд

В команде может не содержаться явных указаний об операнде; в этом случае операнд подразумевается и фактически задается кодом операции команды.

Подразумеваемый адрес

В команде может не содержаться явных указаний об адресе участвующего в операции операнда или адреса, по которому должен быть размещен результат операции, но этот адрес подразумевается.

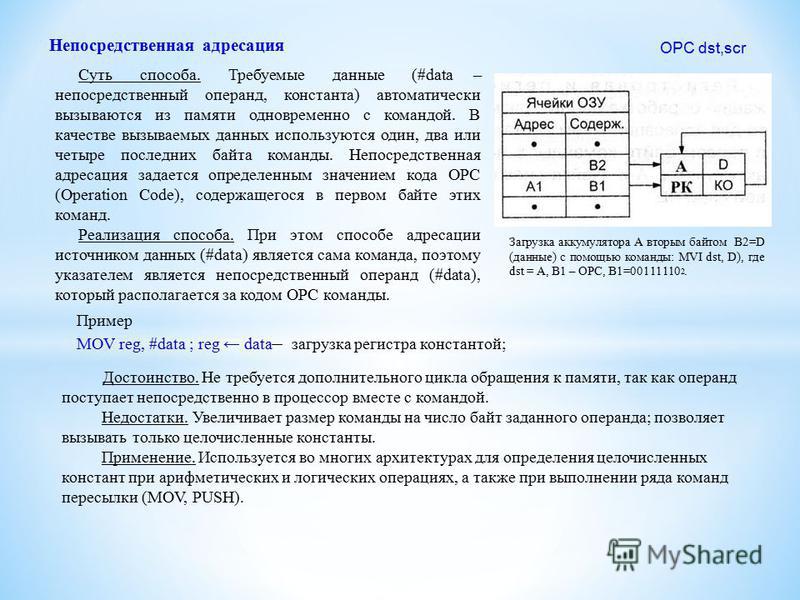

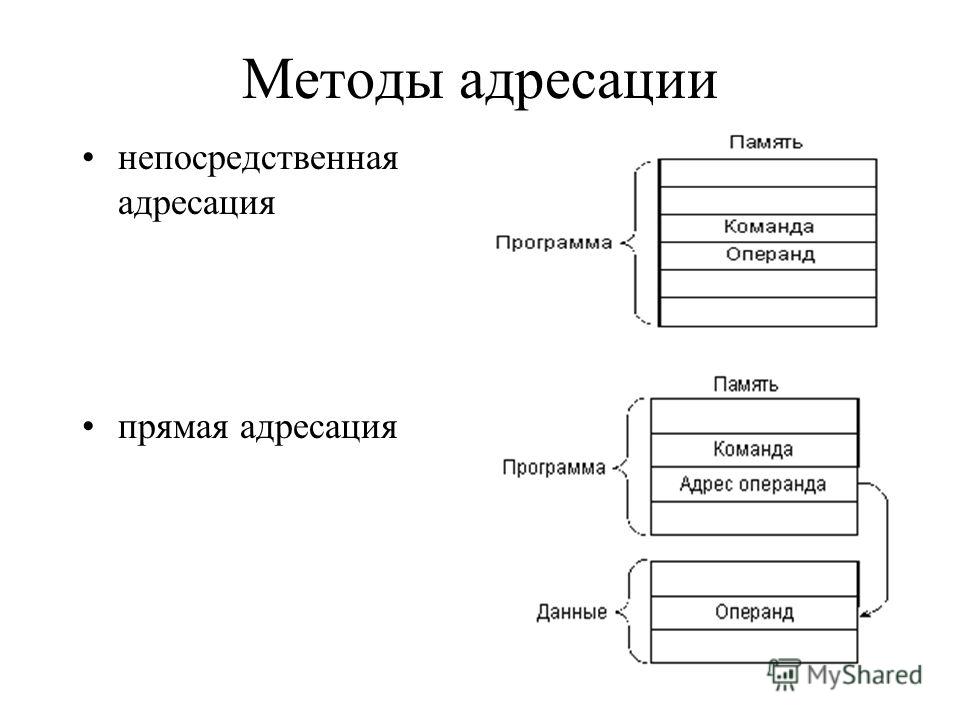

Непосредственная адресация

В команде содержится не адрес операнда, а непосредственно сам операнд. При непосредственной адресации не требуется обращения к памяти для выборки операнда и ячейки памяти для его хранения. Это способствует уменьшению времени выполнения программы и занимаемого ею объёма памяти. Непосредственная адресация удобна для хранения различного рода констант.

Непосредственная адресация удобна для хранения различного рода констант.

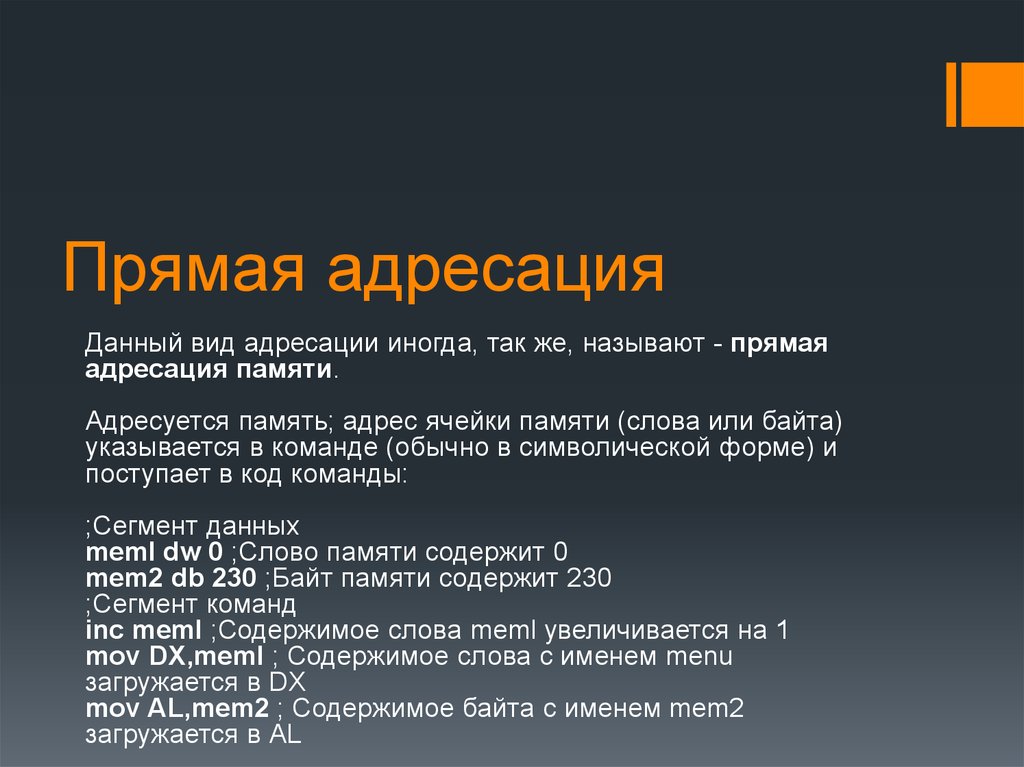

Прямая адресация

Адрес указывается непосредственно в виде некоторого значения, все ячейки располагаются на одной странице. Преимущество этого способа в том, что он самый простой, а недостаток — в том, что разрядность регистров общего назначения процессора должна быть не меньше разрядности шины адреса процессора.

Относительная (базовая) адресация

При этом способе адресации исполнительный адрес определяется как сумма адресного кода команды и базового адреса, как правило хранящегося в специальном регистре — регистре базы.

Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом регистре выбирают таким, чтобы можно было адресовать любую ячейку оперативной памяти, а адресный код команды используют для представления лишь сравнительно короткого «смещения». Смещение определяет положение операнда относительно начала массива, задаваемого базовым адресом.

Укороченная адресация

В адресном поле командного слова содержатся только младшие разряды адресуемой ячейки. Дополнительный указательный регистр.

- Адресация с регистром страницы является примером сокращённой адресации. При этом вся память разбивается на блоки-страницы. Размер страницы диктуется длиной адресного поля.

Регистровая адресация

Регистровая адресация является частным случаем укороченной. Применяется, когда промежуточные результаты хранятся в одном из рабочих регистров центрального процессора. Поскольку регистров значительно меньше чем ячеек памяти, то небольшого адресного поля может хватить для адресации.

Косвенная адресация

Адресный код команды в этом случае указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Косвенная адресация широко используется в малых и микроЭВМ, имеющих короткое машинное слово, для преодоления ограничений короткого формата команды (совместно используются регистровая и косвенная адресация).

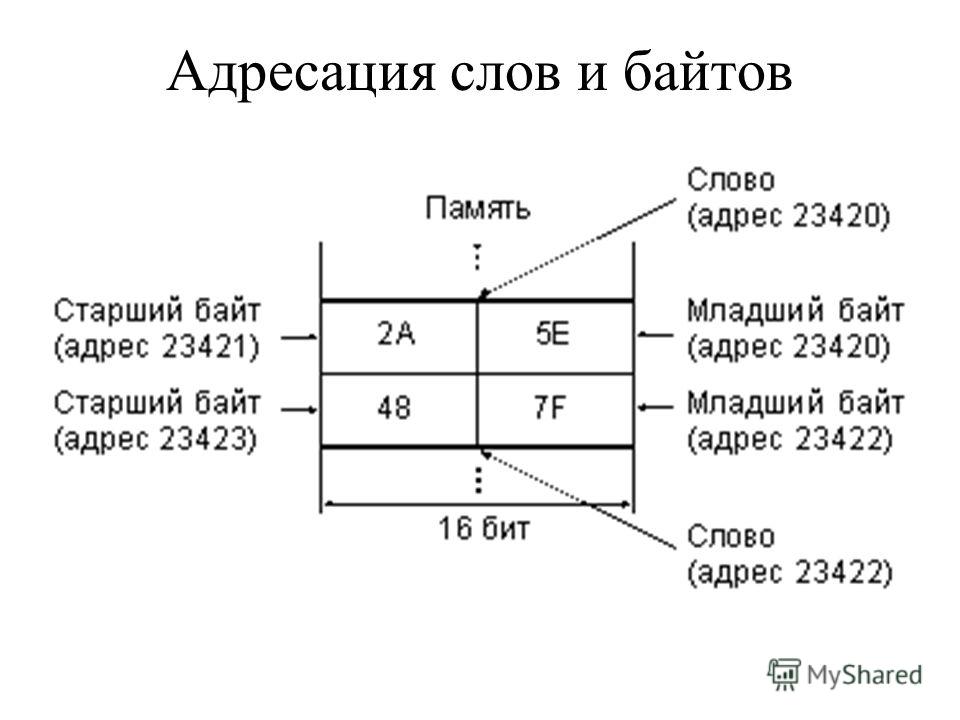

Адресация слов переменной длины

Эффективность вычислительных систем, предназначенных для обработки данных, повышается, если имеется возможность выполнять операции со словами переменной длины. В этом случае в машине может быть предусмотрена адресация слов переменной длины, которая обычно реализуется путем указания в команде местоположения в памяти начала слова и его длины.

Стековая адресация

Стековая память, реализующая безадресное задание операндов, особенно широко используется в микропроцессорах и Мини-ЭВМ.

Автоинкрементная и автодекрементная адресации

Поскольку регистровая косвенная адресация требует предварительной загрузки регистра косвенным адресом из оперативной памяти, что связано с потерей времени, такой тип адресации особенно эффективен при обработке массива данных, если имеется механизм автоматического приращения или уменьшения содержимого регистра при каждом обращении к нему. Такой механизм называется соответственно автоинкрементной и автодекрементной адресацией. В этом случае достаточно один раз загрузить в регистр адрес первого обрабатываемого элемента массива, а затем при каждом обращении к регистру в нём будет формироваться адрес следующего элемента массива.

В этом случае достаточно один раз загрузить в регистр адрес первого обрабатываемого элемента массива, а затем при каждом обращении к регистру в нём будет формироваться адрес следующего элемента массива.

При автоинкрементной адресации сначала содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива. При автодекрементной адресации сначала содержимое указанного в команде регистра уменьшается на число байт в элементе массива, а затем используется как адрес операнда.

Автоинкрементная и автодекрементная адресации могут рассматриваться как упрощенный вариант индексации — весьма важного механизма преобразования адресных частей команд и организации вычислительных циклов, поэтому их часто называют автоиндексацией.

Индексация

Для реализуемых на ЭВМ методов решения математических задач и обработки данных характерна цикличность вычислительных процессов, когда одни и те же процедуры выполняются над различными операндами, упорядоченно расположенными в памяти. Поскольку операнды, обрабатываемые при повторениях цикла, имеют разные адреса, без использования индексации требовалось бы для каждого повторения составлять свою последовательность команд, отличающихся адресными частями.

Поскольку операнды, обрабатываемые при повторениях цикла, имеют разные адреса, без использования индексации требовалось бы для каждого повторения составлять свою последовательность команд, отличающихся адресными частями.

Программирование циклов существенно упрощается, если после каждого выполнения цикла обеспечено автоматическое изменение в соответствующих командах их адресных частей согласно расположению в памяти обрабатываемых операндов. Такой процесс называется модификацией команд, и основан на возможности выполнения над кодами команд арифметических и логических операций.

См. также

- Страничная память

- Сегментная адресация памяти

- Блок управления памятью

Примечания

- ↑ СТ ИСО 2382/7-77 // Вычислительная техника. Терминология: Справочное пособие. Выпуск 1 / Рецензент канд. техн. наук Ю. П. Селиванов. — М.: Издательство стандартов, 1989. — 168 с. — 55 000 экз. — ISBN 5-7050-0155-X

- ↑ 1 2 Першиков В.

И., Савинков В. М. Толковый словарь по информатике / Рецензенты: канд. физ.-мат. наук А. С. Марков и д-р физ.-мат. наук И. В. Поттосин. — М.: Финансы и статистика, 1991. — 543 с. — 50 000 экз. — ISBN 5-279-00367-0

И., Савинков В. М. Толковый словарь по информатике / Рецензенты: канд. физ.-мат. наук А. С. Марков и д-р физ.-мат. наук И. В. Поттосин. — М.: Финансы и статистика, 1991. — 543 с. — 50 000 экз. — ISBN 5-279-00367-0

Литература

- Ю. М. Казаринов. Микропроцессоры в радиотехнических системах.

| Это заготовка статьи о компьютерах. Вы можете помочь проекту, исправив и дополнив её. Это примечание по возможности следует заменить более точным. |

режимов адресации памяти | What, Number, Types & Examples

Ресурсы памяти и хранения данных GCSE (14-16 лет)

- Редактируемая презентация урока в PowerPoint

- Редактируемые раздаточные материалы

- Глоссарий, который охватывает ключевые термины модуля

- Тематические карты памяти для визуализации ключевых понятий

- Карточки для распечатки, помогающие учащимся активно вспоминать и уверенно повторять

- Тест с ответами для проверки знаний и понимания модуля

Просмотр ресурсов памяти и хранения данных GCSE

Ресурсы хранения данных уровня A (16-18 лет)

- Редактируемая презентация урока в PowerPoint

- Тематические карты памяти для визуализации ключевых понятий

- Печатные карточки, помогающие учащимся активно вспоминать и повторять на основе уверенности

- Тест с прилагаемыми ключами для ответов для проверки знаний и понимания модуля

Просмотр хранилища данных уровня A

1 Память и ресурсы хранения данных GCSE (14–16 лет)

2 Ресурсы хранения данных уровня A (16–18 лет)

3 Что такое режим адреса памяти?

4 Количество режимов адресации

5 Наблюдение за методами для 8086 правила разделены на 2 класса:

6 Типы режимов адресации

7 Различные режимы адресации

8 Индексный режим

из 9 С учетом переноса контроль, слежение за методами:

10 Последующие режимы адресации

11 Компьютерные процессоры, в которых не используется последовательное выполнение

12 Условные выполнения

13 Относительный режим адресации

14 Преимущества режима адресации

15 Использование адресов адресов:

160019.

Что такое режим адреса памяти?

Режим адресации — это способ указания операнда инструкции. Данные, хранящиеся в коде операции, являются значением операнда или результатом. Роль микропроцессора заключается в выполнении ряда сохраненных в памяти инструкций для выполнения конкретной задачи. Для работы необходимы:

- Администратор или код операции, который указывает, что делать

- Операнды, отображающие информацию, которая будет использоваться в методе

Например, если бы мы каким-то образом включили числа 1 и 2 и получили бы результат, мы бы вероятно, составить это численно как 1 + 2. В этой ситуации наш администратор (+) или расширение, а числа 1 и 2 являются нашими операндами. Важно сообщить машине в микропроцессоре, как получить операнды для выполнения задачи. Слово, определяющее адрес операнда, хранящегося в памяти, является эффективным адресом. Существует множество способов определения или получения действующего адреса таких операторов непосредственно из реестра. Такие подходы известны как режимы адресации. Программисты обычно пишут на языке высокого уровня, так как это простой способ описать переменные и операции, которые программист должен выполнять над переменными.

Такие подходы известны как режимы адресации. Программисты обычно пишут на языке высокого уровня, так как это простой способ описать переменные и операции, которые программист должен выполнять над переменными.

Позже, для создания компьютерного кода, эта программа компилируется. Он имеет низкоуровневые инструкции для машинного кода. Инструкция низкого уровня имеет операнды и коды операций. Режим адресации не имеет ничего общего с частью кода операции. Основное внимание уделяется представлению в инструкциях адреса операнда. В этом уроке мы собираемся описать некоторые режимы адресации, которые можно использовать, чтобы показать, как можно извлекать операнды. Мы также проиллюстрируем примеры того, как используется каждый режим адресации, и укажем на некоторые особенности этих режимов адресации.

Количество режимов адресации

Что касается количества слежения за режимами, которые они обеспечивают в аппаратном обеспечении, различные модели хитроумных устройств существенно различаются. Хотя вряд ли требуется какой-либо дополнительный заголовок и, возможно, дополнительный регистр, есть несколько идеальных условий, чтобы воздержаться от сложного поиска режимов и использовать только один или несколько более простых методов поиска режимов. Организация процессоров конвейера оказалась намного менее сложной, если правило, доступное для просмотра режимов, является прямым.

Хотя вряд ли требуется какой-либо дополнительный заголовок и, возможно, дополнительный регистр, есть несколько идеальных условий, чтобы воздержаться от сложного поиска режимов и использовать только один или несколько более простых методов поиска режимов. Организация процессоров конвейера оказалась намного менее сложной, если правило, доступное для просмотра режимов, является прямым.

Для большинства структур RISC существует всего около пяти простых режимов преобразования, в то время как модели CISC, например, DEC VAX, имеют более двенадцати режимов преобразования, некоторые из которых вызывают недоумение. Было всего три основных режима для дизайна IBM System / 360; еще пара была включена для System/390.

Основное средство поиска необходимого метода надежно зашифровано в коде подшипника, когда есть только несколько режимов наблюдения. Тем не менее, определенное поле постоянно выделяется на пути, чтобы изобразить режим поиска, когда режимов наблюдения несколько. Принимая во внимание все обстоятельства, все заголовки, DEC VAX допускал различные операнды памяти и, следовательно, сохранял скрытые почти любые части каждого спецификатора операнда, чтобы показать наблюдение за путем для этого конкретного операнда.

Сохранение частей спецификатора наблюдения за режимом, отключенным от битов активности кода операции, обеспечивает равномерное расположение правил. Действительно, даже на машине с несколькими режимами, оценки реальных проектов показывают, что ровно 90% или больше всех используемых режимов относятся к основным режимам, указанным ниже. Поскольку большинство таких подсчетов зависит от кода, созданного компиляторами из диалектов значительного уровня, это в некоторой степени говорит об ограничениях используемых компиляторов.

Отслеживание методов для правил 8086 разделено на 2 класса:

- Информация о методах адресации

- Режимы адресации ветвей

Универсальное разрешение памяти предоставляется памятью 8086, отслеживающей режимы, что позволяет вам эффективно добраться до факторов, шоу, записей, указателей и других сложных видов данных. Правильное использование режимов адресации памяти — секрет успешного программирования на ассемблере. Два компонента инструкции программы на ассемблере — это

Типы режимов адресации

- Режим адресации регистрации

- Режим прямого адресации

- Режим непосредственной обработки

- Регистр режима режима непрямой адресации

- Режим адресации

- Режим Auto Increment

- Auto Mode

- Reliving Addicing Mode

- Auto Mode

- RELEDINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGINGIN

Новаторская область или смещение: правильная область — это область определенной области памяти, где доступно отношение операнда.

Включая любое сочетание трех сегментов области: удаление, основание и изложение, достигается баланс.

Включая любое сочетание трех сегментов области: удаление, основание и изложение, достигается баланс.Различные режимы адресации

Различные способы отслеживания режимов используются 8086, что продемонстрировано различными методами описания операнда микросхемы 8086.

Отслеживание режимов, используемых микрочипами 8086, анализируются ниже: режим

Данные доступны в этом методе в поле области направления. Заполняется как план-направление по одному району.

Примечание: Во втором режиме урон в том, что количество констант ограничено областью

Косвенный режим:

В режиме косвенной адресации регистров адрес операнда помещается в любой из регистров. Инструкция указывает регистр, который содержит адрес операнда. Две памяти получают возможность (получить адрес операнда и привести отношение к операнду) необходимы для получения оценки операнда.

Пример: SPIM/SAL – показывать указатели и закулисные регистры:

- .

data или. Данные

data или. Данные - Массив 1: 1,2,3,4,5,6,6 байт

- .text: Text

- начало:

- La $3, array1 # array1 — режим подсказки для стремления к

- Add $3, $3,4 # Измерение площади пятой части

- Sb $0, ($3) # array1[ 4] = 0 байт с индукцией к массиву1[4]

- # закулисная стратегия для стремления к

- Косвенный режим бывает двух видов, о чем свидетельствует наличие эффективного адреса:

Закулисный регистр: продуктивная область находится в регистре в этом режиме, и имя соответствующего регистра хранится в поле области направления. Косвенная память: в этом режиме новаторская область обрабатывается в памяти, а просмотр адреса памяти обрабатывается в поле области запроса.

Здесь для доступа к данным требуются две ссылки на память.

Непрямая память:

Некоторые из ищущих методов, упомянутых в этой композиции, могут иметь дополнительную часть, чтобы показать обходной путь, например, область, выбранная с использованием некоторого режима, подтверждает область регион (обычно жесткое и быстрое слово), который содержит реальную разумную территорию.

Аномальная тенденция может быть использована для кода или информации. Он может использовать указатели, ссылки или манипуляторы, которые в принципе менее непредсказуемы, и может, кроме того, проще выполнять подпрограммы, которые ни при каких условиях не могут быть адресованы. Карусель, как правило, дисциплинирует знакомство из-за включенного дополнительного метода памяти.

Некоторые древние маленькие компьютеры (например, DEC PDP-8, Data General Nova) имели небольшое количество регистров и просто стремились к работе (8 штук). Начиная с сегодняшнего дня и в обозримом будущем, использование памяти в обратном порядке было почти основной стратегией для определения любого основного объема памяти.

Прямая адресация:

Баланс операнда указывается в руководстве как 8-разрядный или 16-тактный компонент удаления. 16-тактовое жизнеспособное расположение информации важно для руководства в этом режиме.

Здесь, чтобы получить информацию, требуется только одно действие обращения к памяти.

Индексный режим

Индексный режим используется для доступа к выставке, компоненты которой находятся в прогрессивных областях памяти. Содержание управляющего кода говорит о начальной позиции кластера и оценке регистра записи, а также оценке файла текущего компонента. Адреса имеют два раздела: количество файловых регистров и постоянный. Расположение операнда — это целостность согласованности и содержание регистра списка. Он содержит записанные (прямые) тенденции, упорядоченные оперативные тенденции и перечисленные аберрантные тенденции.

Автоматически индексированный (режим приращения)

Мощное местоположение операнда — это содержание регистра, указанного в руководстве. Содержание этого регистра, следовательно, увеличивается после достижения операнда, указывающего на следующую последовательную позицию памяти. (R1) из +.

Важно для прогулок по выставкам. R2 – инициализация отображения d – размер сегмента.

Автоматический запрос (метод уменьшения)

Убедительная область операнда представляет собой содержимое регистра, показанного в направлении.

Содержание этого регистра обычно сокращается, чтобы отображать прошлую прогрессивную позицию памяти до того, как будет получен операнд. — (R1)

Содержание этого регистра обычно сокращается, чтобы отображать прошлую прогрессивную позицию памяти до того, как будет получен операнд. — (R1)Для доступа к данным здесь требуется 1 ссылка на регистр, 1 ссылка на память и 1 перемещение АЛУ.

Режим механизированного уменьшения сравним с методом механизированного уменьшения. Оба могут также использоваться как push и fly для выполнения стека. Для выполнения информационных структур «Назад-в-первый-выход» ценны режимы автоматического увеличения и автоматического уменьшения.

Принимая во внимание передачу контроля, отслеживание методов:

PC сравнительное отслеживание метода

PC сравнительное отслеживание метода используется для подтверждения межрегионального перемещения управления, здесь область убеждения полученный путем смешивания вытеснения к счетчику программ.

EA= ПК + поле адреса

ПК= ПК + относительная стоимость.

Реестр Фонда в поисках метода:

Метод наблюдения за базовым регистром используется для завершения между перемещениями управления пакетами.

В этом режиме, увеличивая оценку поля зоны, получается продуктивная зона.

В этом режиме, увеличивая оценку поля зоны, получается продуктивная зона.EA = регистр основания + адресное поле.

ПК = регистр основания + относительная стоимость.

Обратите внимание:

- Для перемещения программы во время выполнения разумно использовать относительный и локальный регистр ПК, оба из которых отслеживают режимы.

- Самый простой способ написать независимые от местоположения коды — использовать режим адресации базового регистра.

Последующие режимы адресации

Последующий запуск

+——+

| нет | запустить сопроводительное руководство

+——+

(адрес счетчика рабочих программ = адрес последовательного руководства)

После выполнения последовательного руководства ЦП незамедлительно выполняет сопровождающее руководство. Последовательное выполнение не рассматривается как режим на определенных ПК.

Большинство рекомендаций по большинству конструкций ЦП являются последовательными направлениями.

Поскольку большинство направлений являются последовательными рекомендациями, создатели ЦП часто включают в себя основные моменты, которые намеренно ограничивают выполнение в разных направлениях — направлениях ветвления — чтобы эти последовательные направления выполнялись быстрее.

Поскольку большинство направлений являются последовательными рекомендациями, создатели ЦП часто включают в себя основные моменты, которые намеренно ограничивают выполнение в разных направлениях — направлениях ветвления — чтобы эти последовательные направления выполнялись быстрее.Запрещающие переходы загружают ПК с одним из двух ожидаемых результатов, в зависимости от условия — большинство моделей ЦП используют какой-либо другой режим отслеживания для «занятого» перехода и прогрессивное выполнение для «незанятого» перехода.

Различные функции современных процессоров — идеальное направление и более сложная конвейерная обработка, ошибочное выполнение и т. д. — поддерживают иллюзию того, что каждое направление заканчивается раньше, чем начинается соседнее, давая сравнимые бесспорные результаты, независимо от того, что на самом деле это не так. что происходит внутри. Каждый «базовый квадрат» таких последовательных пеленгов показывает как временную, так и пространственную локаль отсчета.

Компьютерные процессоры, не использующие последовательное выполнение

Существуют особенно редкие процессоры, которые не используют последовательное выполнение с программным счетчиком. В каждом руководстве по конкретным процессорам часто указывается местонахождение следующего руководства. Такие ЦП имеют указатель направления, который удерживает определенное местоположение; это не что иное, как счетчик программы, поэтому нет возможности его расширить. Некоторые компьютеры с барабанной памятью присоединяются к таким процессорам, как IBM 650, блок SECD и RTX 32P. Другие вычислительные структуры идут значительно дальше, используя различные опции, в отличие от счетчика программ, стремясь преодолеть узкое место фон Неймана.

Условное выполнение

Некоторые модели ПК имеют условные направления (например, ARM, однако больше не в 64-тактном режиме для всех рекомендаций) или направления с ограничительной нагрузкой (например, x86), которые могут сделать условные ветви повторяющимися время от времени и не допускайте промывки трубопровода наведения.

Юбка имеет тенденцию рассматриваться как потрясающий вид ПК-родственника, уделяющий особое внимание режиму с фиксированным балансом «+1». Как и ПК-родственники, несколько процессоров имеют наборы этого контроля для режимов, которые в основном предлагают один регистр («пропустить, если reg1 = 0») или не использовать регистры, определенно подразумевая некоторый последний установленный фрагмент в регистре состояния. У различных процессоров есть ассортимент, который выбирает определенную цифру в определенном байте для проверки («пропустить в любой точке цикла 7 из reg12, равного 0»).

Юбка имеет тенденцию рассматриваться как потрясающий вид ПК-родственника, уделяющий особое внимание режиму с фиксированным балансом «+1». Как и ПК-родственники, несколько процессоров имеют наборы этого контроля для режимов, которые в основном предлагают один регистр («пропустить, если reg1 = 0») или не использовать регистры, определенно подразумевая некоторый последний установленный фрагмент в регистре состояния. У различных процессоров есть ассортимент, который выбирает определенную цифру в определенном байте для проверки («пропустить в любой точке цикла 7 из reg12, равного 0»).В отличие от всех других неожиданных ответвлений, заголовок «пропустить» никогда не нужно очищать конвейер курса, во всяком случае, он может потребовать игнорирования движения с направлением.

Режим относительной адресации

Мы рассмотрели режим индексной адресации в материале выше. Там для обращения к адресу следующего операнда мы добавили константу в текст реестра. В некоторых машинах вместо регистра используется программный счетчик.

Символическое представление режима относительного адреса:

X(PC)

Эффективный адрес для него будет:

EA = X + (PC)

Как и здесь, по отношению к программному счетчику определяются адреса операндов. Вот почему он называется режимом относительного адреса.

Преимущество: режим относительной адресации не требует обращения к памяти.

Недостаток: Режим относительной адресации как таковой не имеет недостатков.

В компьютерной архитектуре все дело в режимах адресации. Это дает нам универсальный способ определения адреса операндов, используемых в инструкции. Разница между режимами адресации на основе памяти и регистров: Доступны различные режимы адресации, и какой из методов адресации можно использовать, зависит от архитектуры и организации ЦП.

РЕЖИМЫ АДРЕСАЦИИ НА ОСНОВЕ ПАМЯТИ РЕЖИМЫ АДРЕСАЦИИ НА ОСНОВЕ РЕГИСТРОВ В памяти операнд доступен, и его адрес находится здесь, в самой инструкции.  Этот метод адресации правильно использует адрес памяти, например. Метод прямой адресации

Этот метод адресации правильно использует адрес памяти, например. Метод прямой адресацииВ одном из регистров будет указан операнд и в инструкции будет дан номер регистра. Операнд извлекается с номером регистра, присутствующим в инструкции, например, метод регистрации 9.0298 Адрес памяти, определенный в руководстве, может показать место, где память сохраняет успешное местоположение. В этой ситуации адрес памяти, указанный в руководстве, например, режим косвенной адресации, содержит действительный адрес памяти. Адрес операнда появляется в регистре. Вы можете получить эффективный адрес из содержимого регистра, определенного в инструкции. Возможно, фактический адрес может не являться сущностью реестра. Этот метод использует все преимущества регистров, таких как регистр косвенного режима, Чтобы получить точное местоположение, материал базового регистра применяется к части руководства по местоположению. Базовый регистр используется для захвата исходного местоположения, и сравнение с базовым местоположением задается полем местоположения руководства, например, режим адресации базового регистра .  Если у нас есть таблица данных, и наше программное обеспечение должно просматривать все значения один за другим нам нужно что-то, что уменьшает счетчик/базовый адрес программного обеспечения или какой-то регистр. Поскольку регистр в этой ситуации существенно уменьшен, режим адресации зависит от регистра, т.е. в режиме автоматического уменьшения

Если у нас есть таблица данных, и наше программное обеспечение должно просматривать все значения один за другим нам нужно что-то, что уменьшает счетчик/базовый адрес программного обеспечения или какой-то регистр. Поскольку регистр в этой ситуации существенно уменьшен, режим адресации зависит от регистра, т.е. в режиме автоматического уменьшенияДля того, чтобы приобрести жизнеспособное местоположение, содержание реестра списка добавляется к части местоположения, которая дается в руководстве. Режим записи используется для доступа к группе, части которой размещаются в растущих местах в памяти, например, режим упорядоченного адреса . Если у нас есть таблица данных, и наше программное обеспечение должно последовательно приближаться ко всем значениям, мы должны найти что-нибудь который увеличивает счетчик/регистр программного обеспечения, имеющего базовый адрес, например, в режиме автоматического увеличения. Чтобы получить доступное местоположение, вещество программного счетчика применяется к биту местоположения руководства.  В этой ситуации часть указания местоположения регулярно представляет собой отмеченное число, которое может быть положительным или отрицательным, например, Относительный, стремящийся к режиму

В этой ситуации часть указания местоположения регулярно представляет собой отмеченное число, которое может быть положительным или отрицательным, например, Относительный, стремящийся к режимуРежим адресации на основе регистров обычно используется для настройки регистров на постоянное значение, и этот метод довольно полезная техника, например метод Immediate. Собранная память, имеющая тенденцию к модам, обычно зависит от адреса памяти и вещества, присутствующего в любом месте памяти. Собранные регистры, имеющие тенденцию к режимам, регулярно зависят от регистров и вещества, которое является либо информацией, либо некоторым адресом памяти, присутствующим в определенных регистрах.

Преимущества режимов адресации

Это также можно определить как преимущества использования режима адресации. Предоставить пользователю гибкость программирования, предлагая такие средства, как указатели памяти, счетчики управления циклом, индексирование данных и смещение программы.

Уменьшить количество битов в области указания команд.

Уменьшить количество битов в области указания команд.Использование режимов адресации:

Некоторые модели с набором направлений, например, Intel x86 и его замены, имели новаторское направление направления. Это воспроизводит оценку полезного местоположения операнда, в любом случае, вместо того, чтобы следить за этой территорией памяти, он складывает область, которая могла быть получена в регистре. Это может иметь значение при переходе области части дисплея в режим просмотра. Точно так же это может быть довольно опасной стратегией для достижения большего количества включений, чем в среднем, в одном направлении; например, использование такого направления с учетом режима «база+индекс+баланс» (недвусмысленное внизу) позволяет объединить два регистра и последовательность в один блок в одном направлении.

Ссылки:

- https://www.geeksforgeeks.org

- https://study.com/academy/lesson/addressing-modes-definition-types-examples.html

- http://www.

cs .iit.edu/~cs561/cs350/addressing/addsclm.html

cs .iit.edu/~cs561/cs350/addressing/addsclm.html - https://en.wikipedia.org/wiki/Addressing_mode#Number_of_addressing_modes

- https://binaryterms.com/addressing-modes-and-its- types.html#RelativeAddressingMode

- https://www.geeksforgeeks.org/difference-between-memory-based-and-register-based-addressing-modes/#:~:text=These%20can%20also%20be%20said ,адресация%20поле%20из%20%20инструкция

Адресация памяти

Адресация памяти- Пейджинг памяти:

- Доступно в модели 80386 и выше.

- Позволяет линейный адрес ( виртуальный адрес ) программы, расположенной в любой части физический Память.

- пейджинговый блок управляется регистрами управления микропроцессорами:

- Пейджинг памяти:

- Система пейджинга работает как в реальном, так и в защищенном режиме.

- Он включается установкой ПГ бит на 1 (самый левый бит в CR0 ).

- (Если установлено значение 0, линейные адреса являются физическими адресами).

- CR3 содержит каталог страниц «физический» базовый адрес.

- Значение в этом регистре — один из немногих «физических» адресов, к которым вы когда-либо будете обращаться в работающей системе.

- каталог страниц может находиться на любой границе 4K, поскольку младшие 12 бит адреса установлены в ноль.

- каталог страниц содержит 1024 записи каталога по 4 байта каждая.

- Каждый каталог страниц адрес записи a страница таблица который содержит до 1024 записей.

- Пейджинг памяти:

- Виртуальный адрес разбит на три части: .

- Каталог : Каждый каталог страниц обращается к разделу основной памяти размером 4 МБ. тип=диск>

- Таблица страниц : Каждый страница таблица запись обращается к разделу основной памяти размером 4 КБ. тип=диск>

- Смещение : Указывает байт на странице. тип=диск>

- Пейджинг памяти:

- Пейджинг памяти:

- каталог страниц составляет 4К байт.

- Каждый таблица страниц составляет 4К байт, а их 1024.

- Если все 4 ГБ памяти выгружаются, накладные расходы составляют 4 МБ!

- Текущая схема требует трех обращений к памяти:

- Один к каталог , один к соответствующему таблица страниц и (наконец) один к нужным данным или элементу кода. Ой!

- А Резервный буфер перевода ( TLB ) используется для кэширования записей каталога страниц и таблицы страниц, чтобы уменьшить количество ссылок на память.

- Кроме того, кэш данных используется для хранения недавно использованных блоков памяти.

- Без этих функций производительность системы была бы крайне низкой.

- .

5 Относительная (базовая) адресация

5 Относительная (базовая) адресация