PCI и PCI-X

Для устройств промышленного назначения в начале 1995 года был принят стандарт Compact PCI. Шина Compact PCI (cPCI) разрабатывалась на основе спецификации PCI 2.1. Этот стандарт принят Организацией производителей промышленных компьютеров PCIMG (PCI Industrial Computer Manufacturers Group). Шина отличается поддержкой большого количества слотов: 8 против 4 в обычной PCI. Как и PCI, шина поддерживает 32-битный и 64-битный обмен. Шина обладает всеми возможностями автоконфигурирования, присущими PCI. Кроме того, шина дает возможность программного прочтения «географического адреса» модуля. Географическая адресация дает дополнительную возможность идентификации физического местоположения модуля (хотя его можно определить и по номерам шины и устройства, пользуясь стандартными конфигурационными функциями PCI). Конструктивно платы Compact PCI представляют собой еврокарты высотой 3U (100×160 мм) с двумя коннекторами (J1 и J2) или 6U (233,35×160 мм) с 4–5 коннекторами (J1…J5).

Коннекторы — 7-рядные экранированные штырьковые разъемы с шагом 2 мм между контактами, на кросс-плате — вилка, на модулях — розетки. Поскольку модули (и разъемы) обычно устанавливаются вертикально, ряды удобнее назвать колонками, что и подразумевается ниже.

| Разъем, контакт | № | Ряд | ||||

| a | b | c | d | e | ||

| J2 | 22 | GA4 | GA3 | GA2 | GA1 | GA0 |

| 21 | CLK6 | GND | RSV | RSV | RSV | |

| 20 | CLK5 | GND | RSV | GND | RSV | |

| 19 | GND | GND | RSV | RSV | RSV | |

| 18 | BRSVP2A18 | BRSVP2B18 | BRSVP2C18 | GND | BRSVP2E18 | |

| 17 | BRSVP2A17 | GND | PRST# | REQ6# | GNT6# | |

| BRSVP2A16 | BRSVP2B16 | DEG# | GND | BRSVP2E16 | ||

| 15 | BRSVP2A15 | GND | FAL# | REQ5# | GNT5# | |

| 14 | AD35 | AD34 | AD33 | GND | AD32 | |

| 13 | AD38 | GND | V(I/O) | AD37 | AD36 | |

| 12 | AD42 | AD41 | AD40 | GND | AD39 | |

| 11 | AD45 | GND | V(I/O) | AD44 | AD43 | |

| 10 | AD49 | AD48 | AD47 | GND | AD46 | |

| 9 | AD52 | GND | V(I/O) | AD51 | AD50 | |

| 8 | AD56 | AD55 | AD54 | GND | AD53 | |

| 7 | AD59 | GND | V(I/O) | AD58 | AD57 | |

| 6 | AD63 | AD62 | AD61 | GND | AD60 | |

| 5 | C/BE5# | GND | V(I/O) | C/BE4# | PAR64 | |

| 4 | V(I/O) | BRSVP2B4 | C/BE7# | GND | C/BE6# | |

| 3 | CLK4 | GND | GNT3# | REQ4# | GNT4# | |

| 2 | CLK2 | CLK3 | SYSEN# | GNT2# | REQ3# | |

| 1 | CLK1 | GND | REQ1# | GNT1# | REQ2# | |

| J1 | 25 | 5V | REQ64# | ENUM# | 3. 3V 3V | 5V |

| 24 | AD1 | 5V | V(I/O) | AD0 | ACK64# | |

| 23 | 3.3V | AD4 | AD3 | 5V | AD2 | |

| 22 | AD7 | GND | 3.3V | AD6 | AD5 | |

| 21 | 3.3V | AD9 | AD8 | M66EN | C/BE0# | |

| 20 | AD12 | GND | V(I/O) | AD11 | AD10 | |

| 19 | 3.3V | AD15 | AD14 | GND | AD13 | |

| 18 | SERR# | GND | 3.3V | PAR | C/BE1# | |

| 17 | 3.3V | IPMB_SCL (SDONE)1 | IPMB_SDA (SBO#)1 | GND | PERR# | |

| 16 | DEVSEL# | GND | V(I/O) | STOP# | LOCK# | |

| 15 | 3.3V | FRAME# | IRDY# | BD_SEL# (GND)2 | TRDY# | |

| 12-14 | Зона ключа | — | — | — | — | |

| 11 | AD18 | AD17 | AD16 | GND | C/BE2# | |

| 10 | AD21 | GND | 3. 3V 3V | AD20 | AD19 | |

| 9 | C/BE3# | IDSEL | AD23 | GND | AD22 | |

| 8 | AD26 | GND | V(I/O) | AD25 | AD24 | |

| 7 | AD30 | AD29 | AD28 | GND | AD27 | |

| 6 | REQ# | GND | 3.3V | CLK | AD31 | |

| 5 | BRSVP1A5 | BRSVP1B5 | RST# | GND | GNT# | |

| 4 | IPMB_PWR (BRSVP1A4)1 | HEALTHY# (GND)1 | V(I/O) | INTP | INTS | |

| 3 | INTA# | INTB# | INTC# | 5V | INTD# | |

| 2 | TCK | 5V | TMS | TDO | TDI | |

| 1 | 5V | -12V | TRST# | +12V | 5V | |

1 — Назначение в скобках — для старых версий.

2 — На системном слоте — GND.

В основном сигналы Compact PCI совпадают с сигналами обычной шины PCI, назначение специфических сигналов приведено в следующей таблице.

| Сигнал | Назначение |

| BD_SEL# | Сигнал от модуля о том, что он установлен в слот и питание подано (подается через один из укороченных контактов, который соединяется после всех основных) |

| BRSVxxxx | Зарезервированные на будущее сигналы, шинно разведенные по слотам; xxxx обозначает позиционный номер контакта (BRSVP1A4 — на контакте A4 разъема P1) |

| CLK[0:6], GNT#[0:6], REQ#[0:6] | Сигналы, радиально разводящиеся от разъема J2 системного слота к периферийным (сигналы CLK0, GNT0# и REQ0# расположены на местах CLK, GNT# и REQ# разъема J1) |

| DEG# | Предупреждение о деградации питания |

| ENUM# | Все аппаратные модули установлены, можно производить нумерацию и конфигурирование устройств |

| FAL# | Отказ питания |

| GA0-GA4 | Географический адрес. Коммутацией на «землю» для каждого слота задается его двоичный географический адрес на шасси Коммутацией на «землю» для каждого слота задается его двоичный географический адрес на шасси |

| SMB_SDA, SMB_SCL, | Сигналы шины SMBus (только на системном слоте) |

| SMB_ALERT# | Сигнал прерывания по шине SMBus |

| HEALTHY# | Сигнал от модуля, что он получает нормальное питание (PwrGood) и сигнал его сброса снят |

| INTP, INTS | Прерывания от первичного и вторичного контроллеров IDE |

| IPMB_PWR, | Батарейное питание шины IPMB (Independent Platform Management Bus, независимая последовательная шина управления платформой) |

| IPMB_SCL, IPMB_SDA | Синхронизация и данные шины IPMB |

| PRST# | Push Button Reset, сигнал от кнопки «Сброс» |

| RSV | Резерв на будущее |

| SYSEN# | Идентификация системного слота (на системном слоте контакт заземлен, что позволяет модулю опознать установку в это место) |

| UNC |

PCI и PCI-X

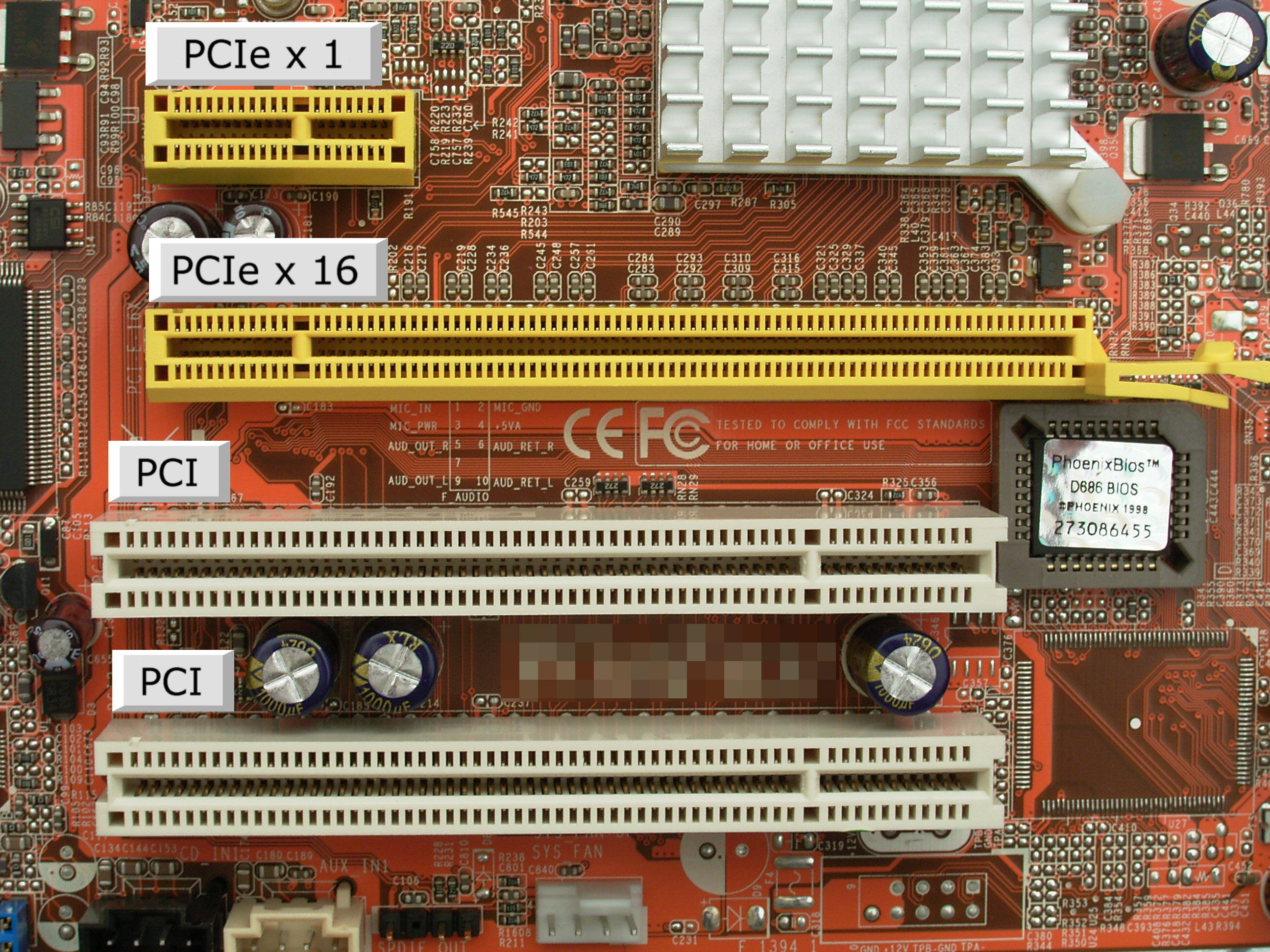

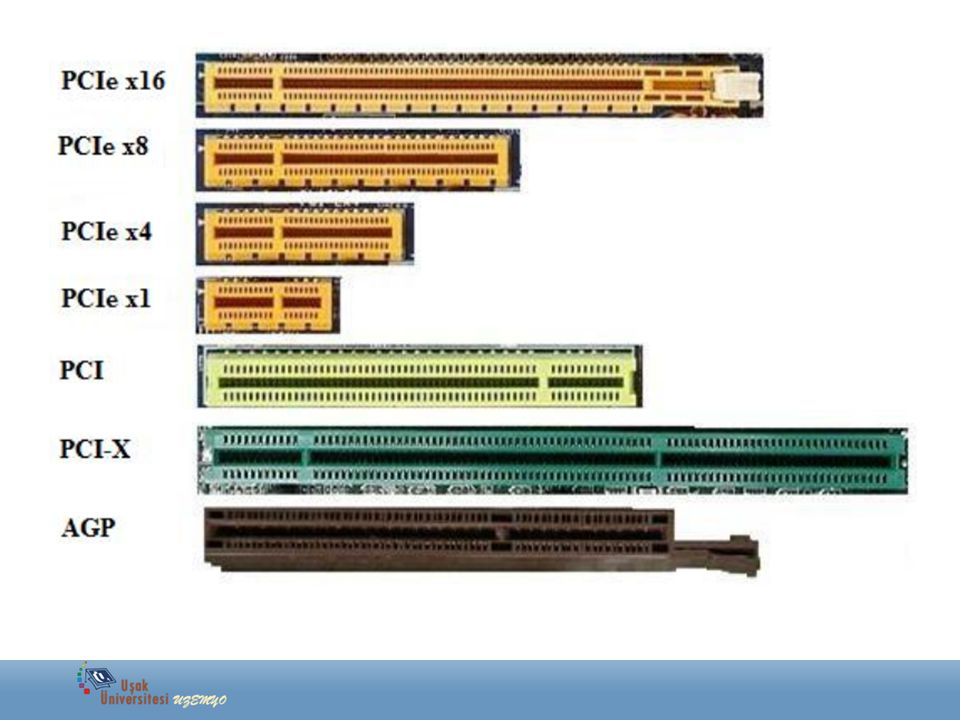

Шины PCI и PCI-X являются основными шинами расширения ввода/вывода в современных компьютерах; для подключения видеоадаптеров их дополняет порт AGP. Шины расширения ввода/вывода (Expansion Bus) являются средствами подключения системного уровня: они позволяют адаптерам и контроллерам периферийных устройств непосредственно использовать системные ресурсы компьютера — пространство адресов памяти и ввода/вывода, прерывания, прямой доступ к памяти. Устройства, подключенные к шинам расширения, могут и сами управлять этими шинами, получая доступ к остальным ресурсам компьютера. Шины расширения механически реализуются в виде слотов (щелевых разъемов) или штырьковых разъемов; для них характерна малая длина проводников, то есть они сугубо локальны, что позволяет достигать высоких скоростей работы. Эти шины могут и не выводиться на разъемы, но использоваться для подключения устройств в интегрированных системных платах.

Шины расширения ввода/вывода (Expansion Bus) являются средствами подключения системного уровня: они позволяют адаптерам и контроллерам периферийных устройств непосредственно использовать системные ресурсы компьютера — пространство адресов памяти и ввода/вывода, прерывания, прямой доступ к памяти. Устройства, подключенные к шинам расширения, могут и сами управлять этими шинами, получая доступ к остальным ресурсам компьютера. Шины расширения механически реализуются в виде слотов (щелевых разъемов) или штырьковых разъемов; для них характерна малая длина проводников, то есть они сугубо локальны, что позволяет достигать высоких скоростей работы. Эти шины могут и не выводиться на разъемы, но использоваться для подключения устройств в интегрированных системных платах.

Поначалу шина PCI вводилась как пристройка (mezzanine bus) к системам с шиной ISA. Она разрабатывалась в расчете на процессоры Pentium, но хорошо сочеталась и с процессорами i486. Позже PCI на некоторое время стала центральной шиной: она соединялась с шиной процессора высокопроизводительным мостом («северным» мостом), входящим в состав чипсета системной платы. Остальные шины расширения ввода/вывода (ISA/EISA или MCA), а также локальная ISAподобная шина X-BUS и интерфейс LPC, к которым подключаются микросхемы системной платы (ROM BIOS, контроллеры прерываний, клавиатуры, DMA, портов COM и LPT, НГМД и прочие «мелочи»), подключались к шине PCI через «южный» мост. В современных системных платах с «хабовой» архитектурой шину PCI отодвинули на периферию, не ущемляя ее в мощности канала связи с процессором и памятью, но и не нагружая транзитным трафиком устройств других шин.

Остальные шины расширения ввода/вывода (ISA/EISA или MCA), а также локальная ISAподобная шина X-BUS и интерфейс LPC, к которым подключаются микросхемы системной платы (ROM BIOS, контроллеры прерываний, клавиатуры, DMA, портов COM и LPT, НГМД и прочие «мелочи»), подключались к шине PCI через «южный» мост. В современных системных платах с «хабовой» архитектурой шину PCI отодвинули на периферию, не ущемляя ее в мощности канала связи с процессором и памятью, но и не нагружая транзитным трафиком устройств других шин.

Шина PCI является синхронной — фиксация всех сигналов выполняется по положительному перепаду (фронту) сигнала CLK. Номинальной частотой синхронизации считается частота 33,3 МГц, при необходимости она может быть понижена. Начиная с версии PCI 2.1 допускается повышение частоты до 66,6 МГц при «согласии» всех устройств на шине. В PCI-X частота может достигать 133 МГц.

В PCI используется параллельная мультиплексированная шина адреса/данных (AD) с типовой разрядностью 32 бит. Спецификация определяет возможность расширения разрядности до 64 бит; в PCI-X версии 2.0 определен также 16-битный вариант шины. При частоте шины 33 МГц теоретическая пропускная способность достигает 132 Mбайт/с для 32-битной шины и 264 Мбайт/с для 64-битной; при частоте синхронизации 66 МГц — 264 Мбайт/с и 528 Мбайт/с соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета: из-за протокольных накладных расходов реальная средняя пропускная способность шины оказывается ниже.

Спецификация определяет возможность расширения разрядности до 64 бит; в PCI-X версии 2.0 определен также 16-битный вариант шины. При частоте шины 33 МГц теоретическая пропускная способность достигает 132 Mбайт/с для 32-битной шины и 264 Мбайт/с для 64-битной; при частоте синхронизации 66 МГц — 264 Мбайт/с и 528 Мбайт/с соответственно. Однако эти пиковые значения достигаются лишь во время передачи пакета: из-за протокольных накладных расходов реальная средняя пропускная способность шины оказывается ниже.

Сравнительные характеристики шин PCI и PCI-X и других шин расширения PCсовместимых компьютеров приведены в табл. 1.1. Шина ISA из настольных компьютеров уходит, но она сохраняет свои позиции в промышленных и встраиваемых компьютерах, как в традиционном, слотовом, так и в «бутербродном» варианте PC/104. В блокнотных компьютерах широко применяются слоты PCMCIA с шинами PC Card и Card Bus. Шина LPC является современным дешевым средством для подключения нересурсоемких устройств к системной плате.

| Шина | Пиковая пропускная способность Мбайт/с | Каналы DMA | Bus-Master | ACFG | Разрядность данных | Разрядность адреса | Частота МгГц |

| ISA-8 | 4 | 3 | — | — | 8 | 20 | 8 |

| ISA-16 | 8 | 7 | + | — | 16 | 24 | 8 |

| LPC | 6,7 | 7 | + | — | 8/16/32 | 32 | 33 |

| EISA | 33,3 | 7 | + | + | 32 | 32 | 8,33 |

| MCA-16 | 16 | — | + | + | 16 | 24 | 10 |

| MCA-32 | 20 | — | + | + | 32 | 32 | 10 |

| VLB | 132 | — | (+) | — | 32/64 | 32 | 33-50(66) |

| PCI | 133-533 | — | + | + | 32/64 | 32/64 | 33/66 |

| PCI-X | 533-4256 | — | + | + | 16/32/64 | 32/64 | 66-133 |

| PCI Express | 496-15872 | — | + | + | 1/2/4/8/12/16/32 | 32/64 | 2,5 ГГц |

| AGP 1x/2x/4x/8x | 266/533/1066/2132 | — | + | + | 32 | 32/64 | 66 |

| PCMCIA | 10/22 | + | — | + | 8/16 | 26 | 10 |

| Card Bus | 132 | — | + | + | 32 | 32 | 33 |

ACFG1 -Поддержка автоматического конфигурирования. Для ISA PnP является поздней надстройкой, реализуемой адаптерами и ПО.

Для ISA PnP является поздней надстройкой, реализуемой адаптерами и ПО.

На что способен формат Mini PCI-e / Хабр

Мне очень нравится формат Mini PCI-e. Это крохотный форм-фактор, служащий базовым для mSATA и M.2, но в основном он используется для подключения карт WiFi и Bluetooth в ноутбуках или маленьких ПК. Но по сути это просто PCI-e, поэтому с его помощью можно сделать гораздо больше.

Вот, к примеру, обычная беспроводная карта, используемая с его помощью:

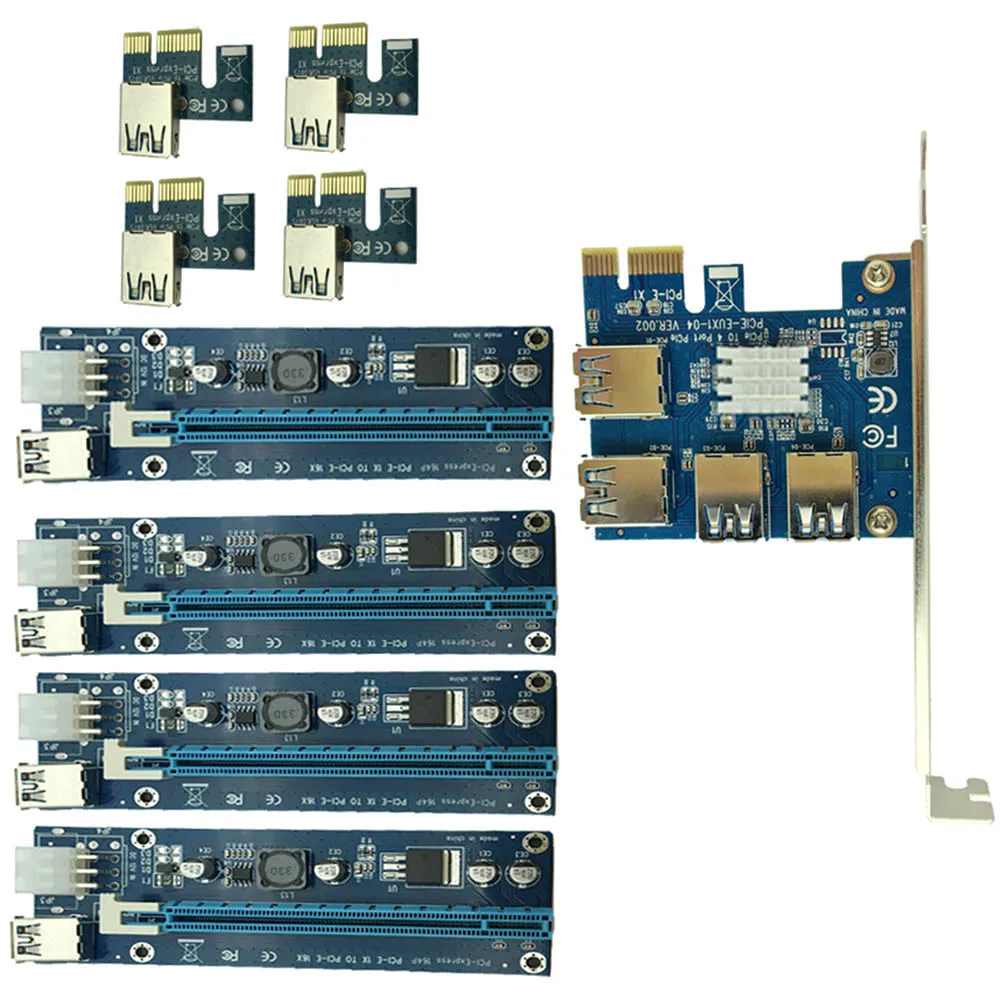

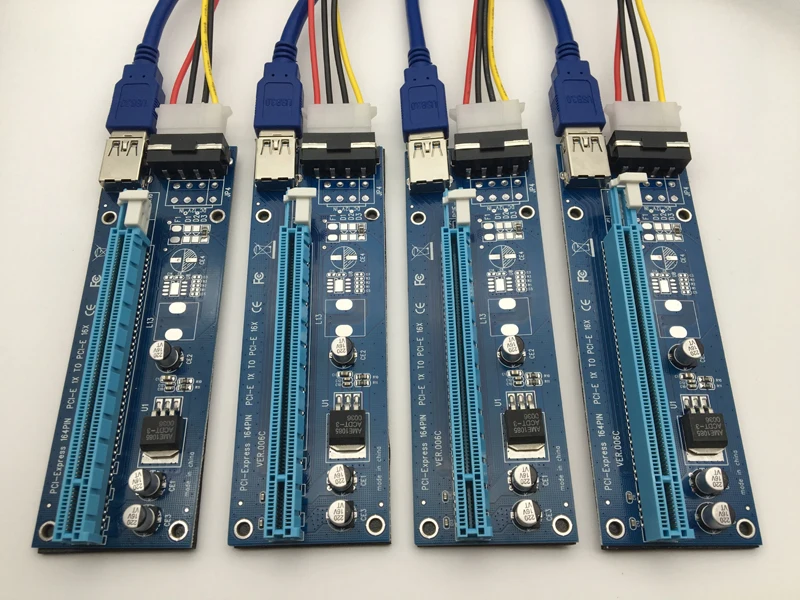

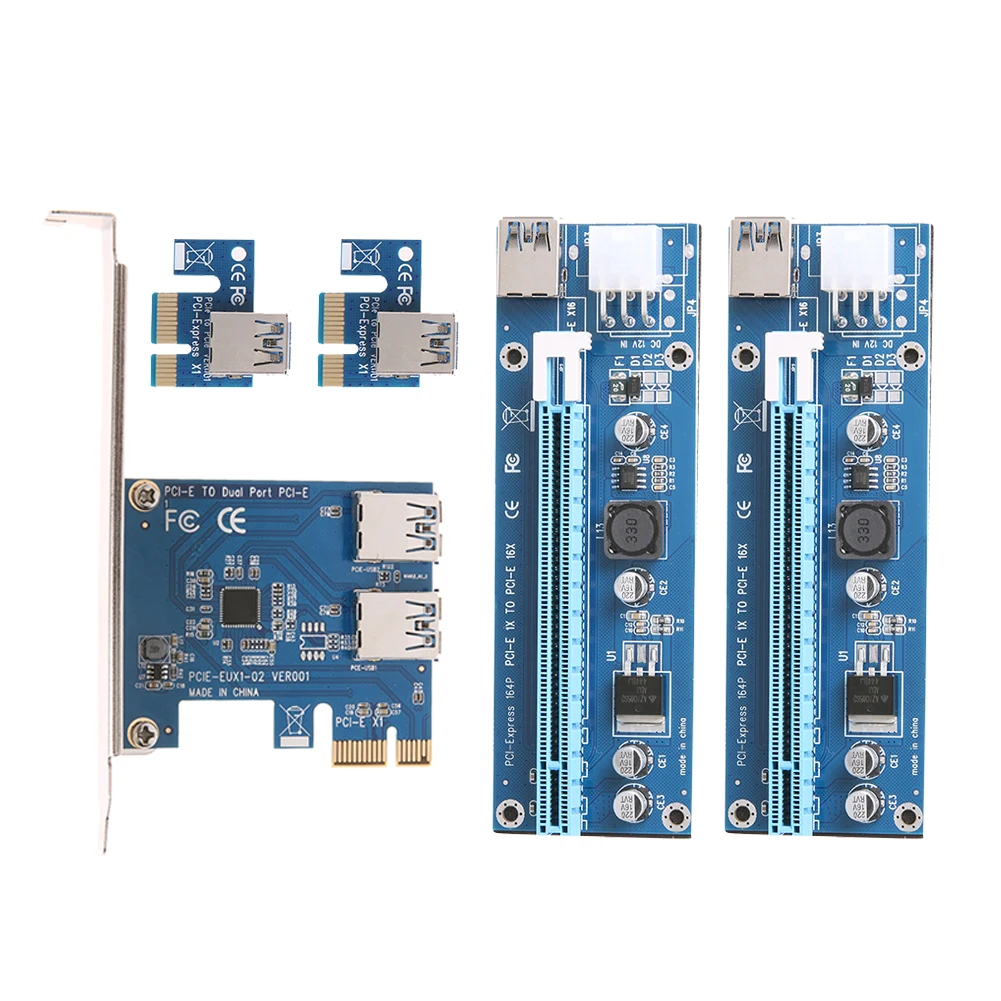

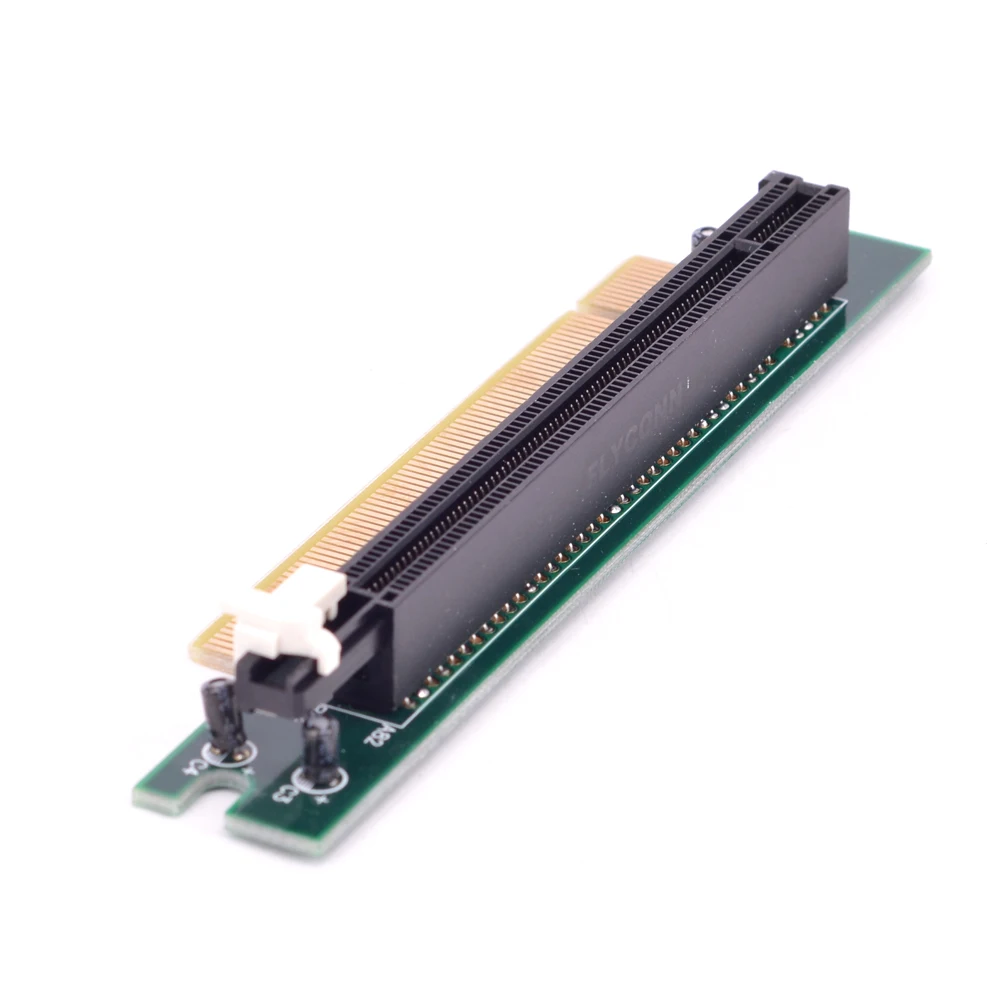

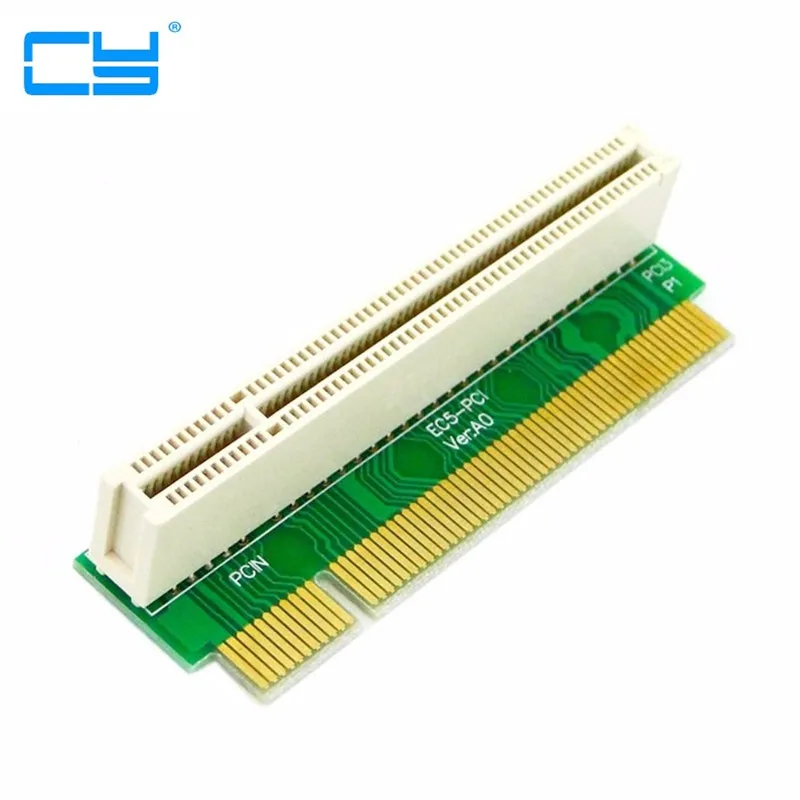

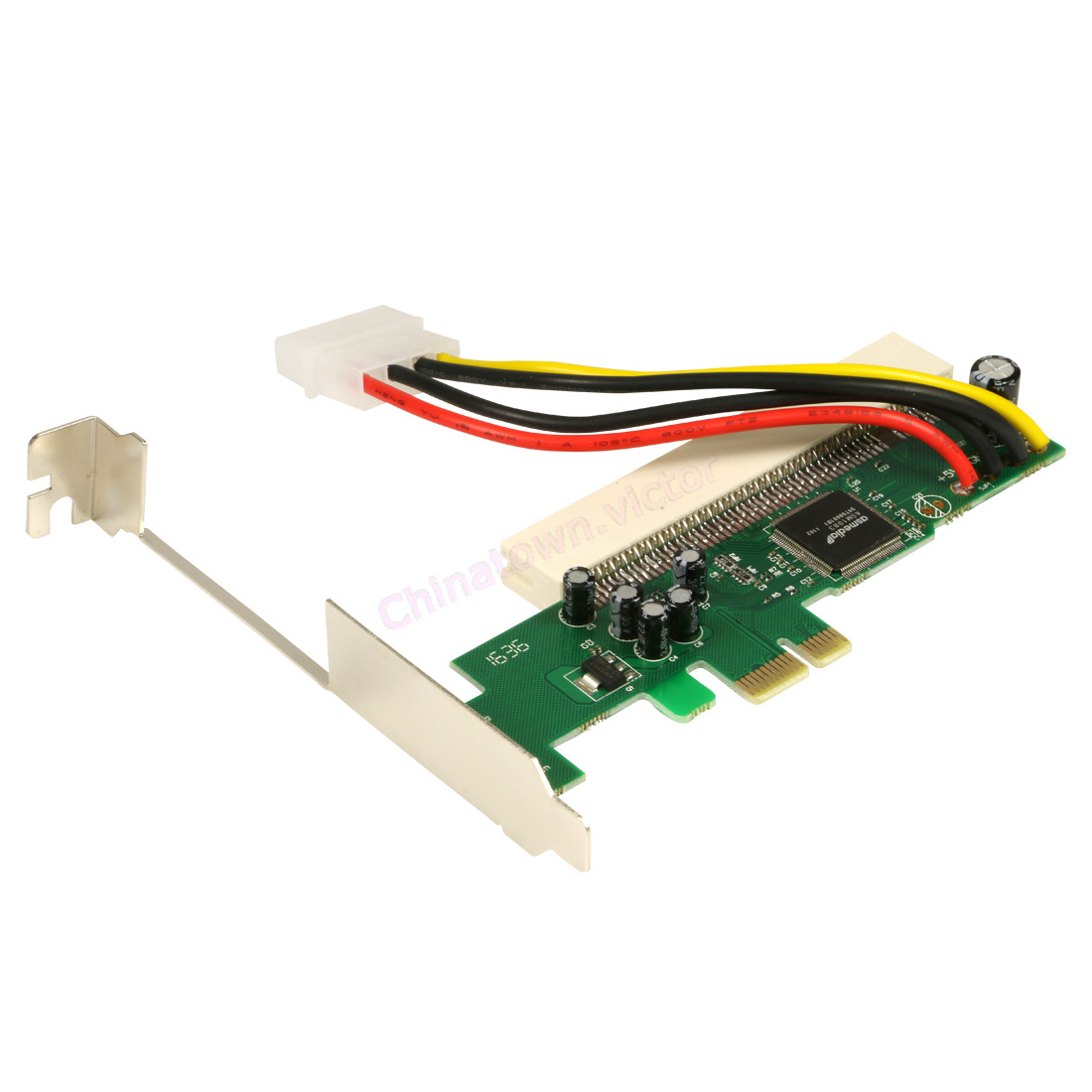

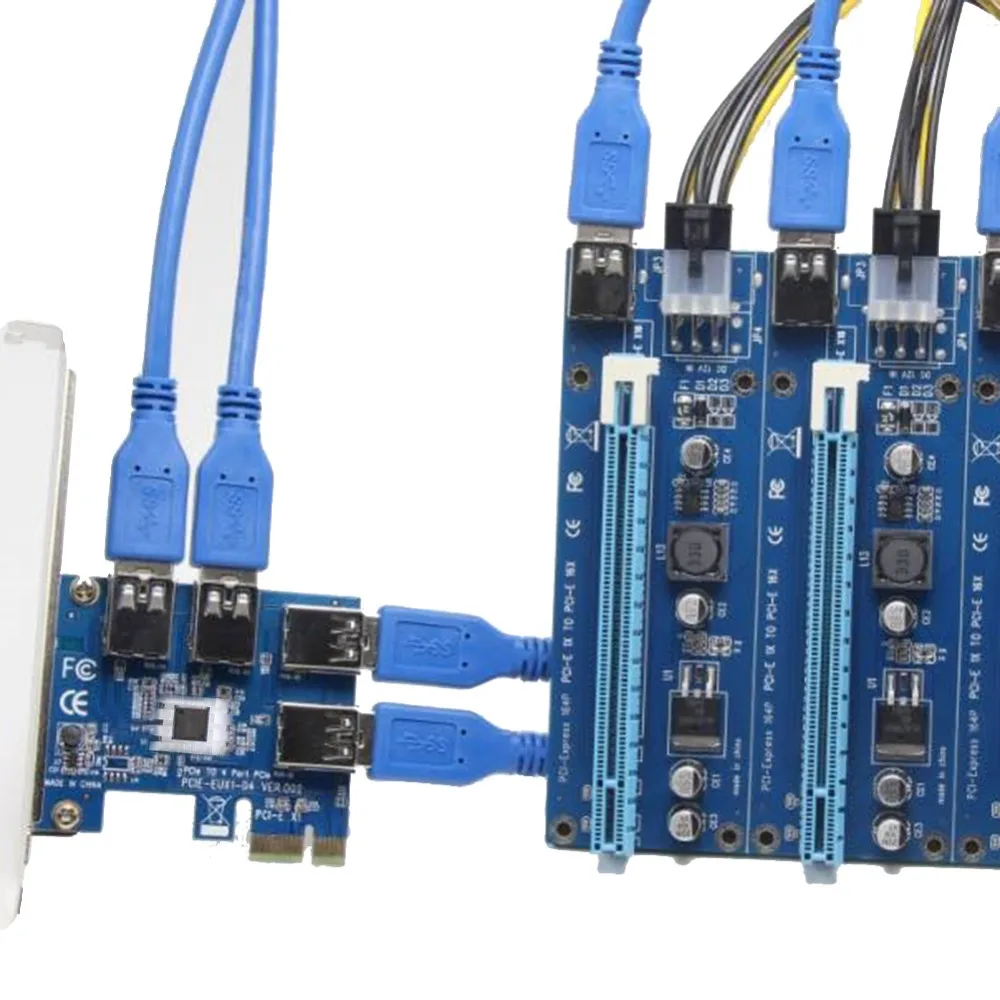

Но так как это просто PCI-e, его можно превратить в PCI-e x1 при помощи адаптера. Это чит-код для Mini PCI-e: после этого туда можно подключить всё, что угодно, вплоть до полноразмерного GPU. Работать будет медленно, но будет.

Однако есть множество карточек, разработанных специально для этого формата. К примеру, карта для Ethernet:

Естественно, диагностические инструменты:

Разъём, конечно же, можно использовать для SATA:

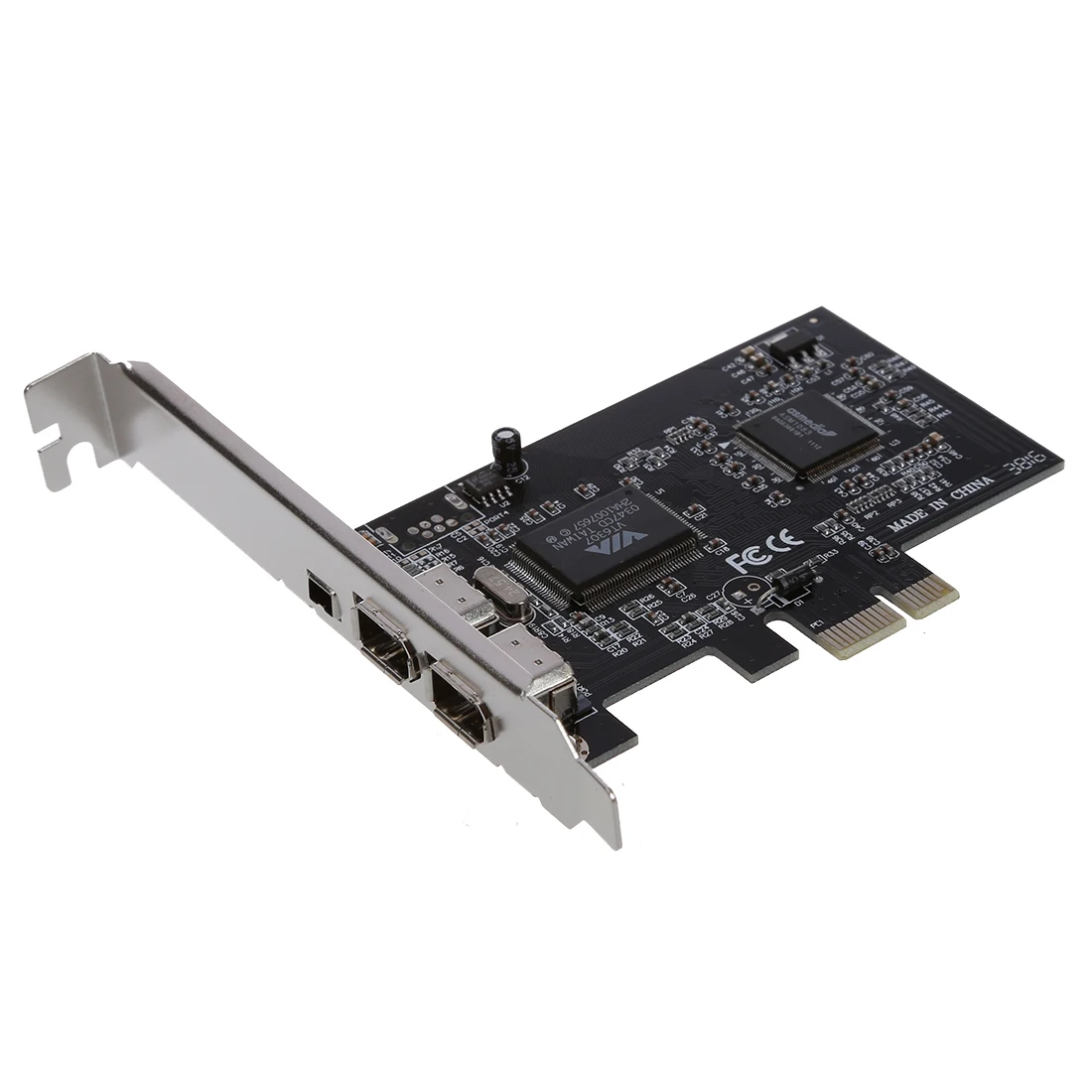

А не хотите ли… Firewire? Что, серьёзно??

Ну если уж нам доступен Firewire, то ничто не мешает использовать USB, если кто-то ещё цепляется за этот устаревающий стандарт:

Естественно, существует и последовательный порт. Промышленный мир работает на интерфейсе RS-232:

Промышленный мир работает на интерфейсе RS-232:

Мало последовательного порта – для вас есть карточка с последовательным и параллельным портами. Иногда ведь хочется подключить к ноутбуку Epson FX-80:

Есть слоты для CompactFlash:

Башни для USB3 сомнительной ценности:

GPS-приёмник, почему-то с отдельной батареей:

И раз уж это PCI-e, он будет достаточно быстрым для видеокарт. Так что они тоже существуют:

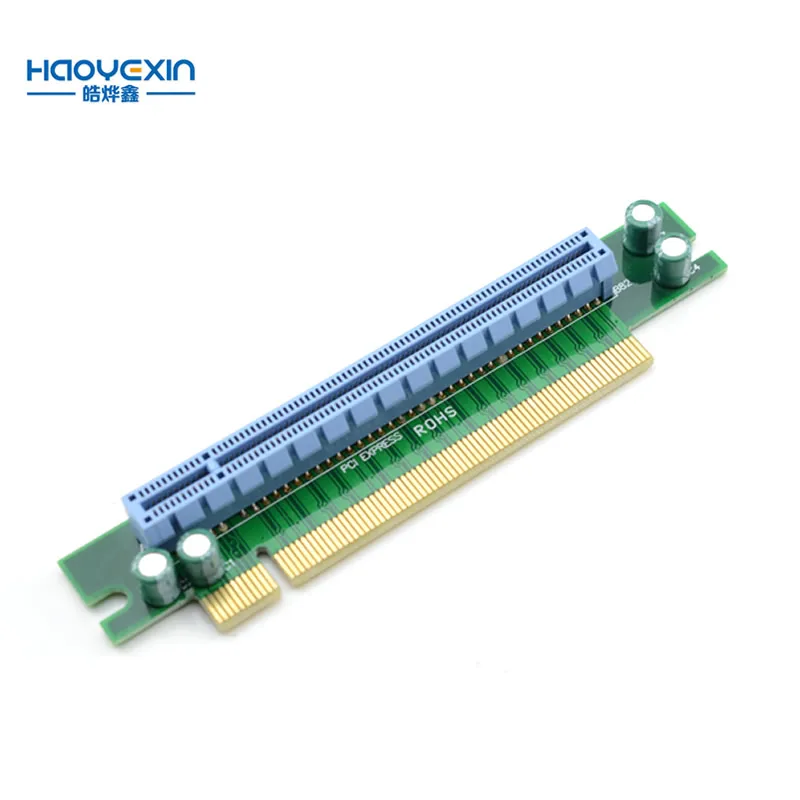

Забавный факт: существуют мосты с PCI-e на PCI. Поэтому, естественно, есть мосты и с Mini PCI-e на PCI – вот, например, такой мост, утыканный звуковыми картами формата PCI:

Как насчёт карточки для приёма сигнала ТВ?

Или SD-слота! Забавно, насколько хорошо слот для SD подходит по размеру для карты Mini PCI-e:

Если вам этого мало, можете взять карту с двумя microSD:

Не желаете ли гигабитного интернета с модулями SFP?

И раз уж есть видеокарты, то есть и звуковые карты:

Или одновременная запись видео с 8 каналов (для камер безопасности):

И, да, гигантская карточка Mini PCI-e со встроенным FPGA:

И двойная шина CAN, если вам вдруг надо будет отладить ваш автомобиль:

А вот вам двойной гигабитный Ethernet, однако в данном случае меня больше веселит, что отдельная дочерняя плата для двух разъёмов Ethernet оказывается больше по размеру платы Mini PCI-e:

А вот адаптер с Mini PCI-e на ExpressCard, чтобы вы могли использовать все эти карточки формата ExpressCard, которых у вас наверняка полно:

Только не путайте его с противоположным переходником с ExpressCard на Mini PCI-e:

А вот такой переходник, с контактами GPIO, специально расположенными в том же порядке, что у Raspberry Pi. Видимо, идея в том, чтобы использовать его с FPGA-компьютерами, оснащёнными Mini PCI-e, совместно с шилдами от Raspberry Pi?

Видимо, идея в том, чтобы использовать его с FPGA-компьютерами, оснащёнными Mini PCI-e, совместно с шилдами от Raspberry Pi?

А вот плата с поддержкой VGA и HDMI, только это не видеокарта, а карта для записи видео:

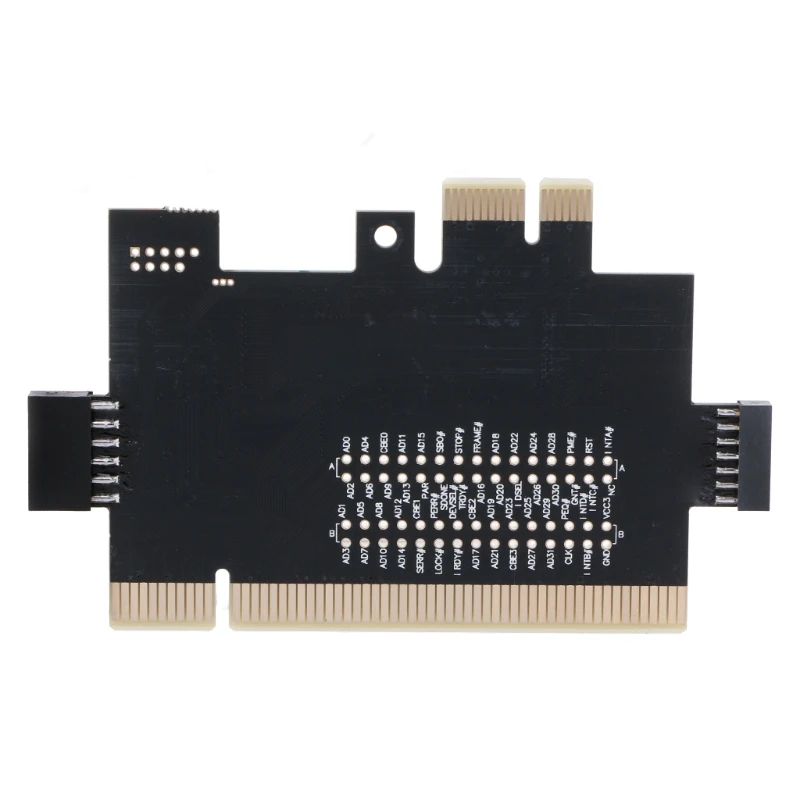

И плата для прототипирования Mini PCI-e, чтобы вы могли разрабатывать собственные карточки для Mini PCI-e:

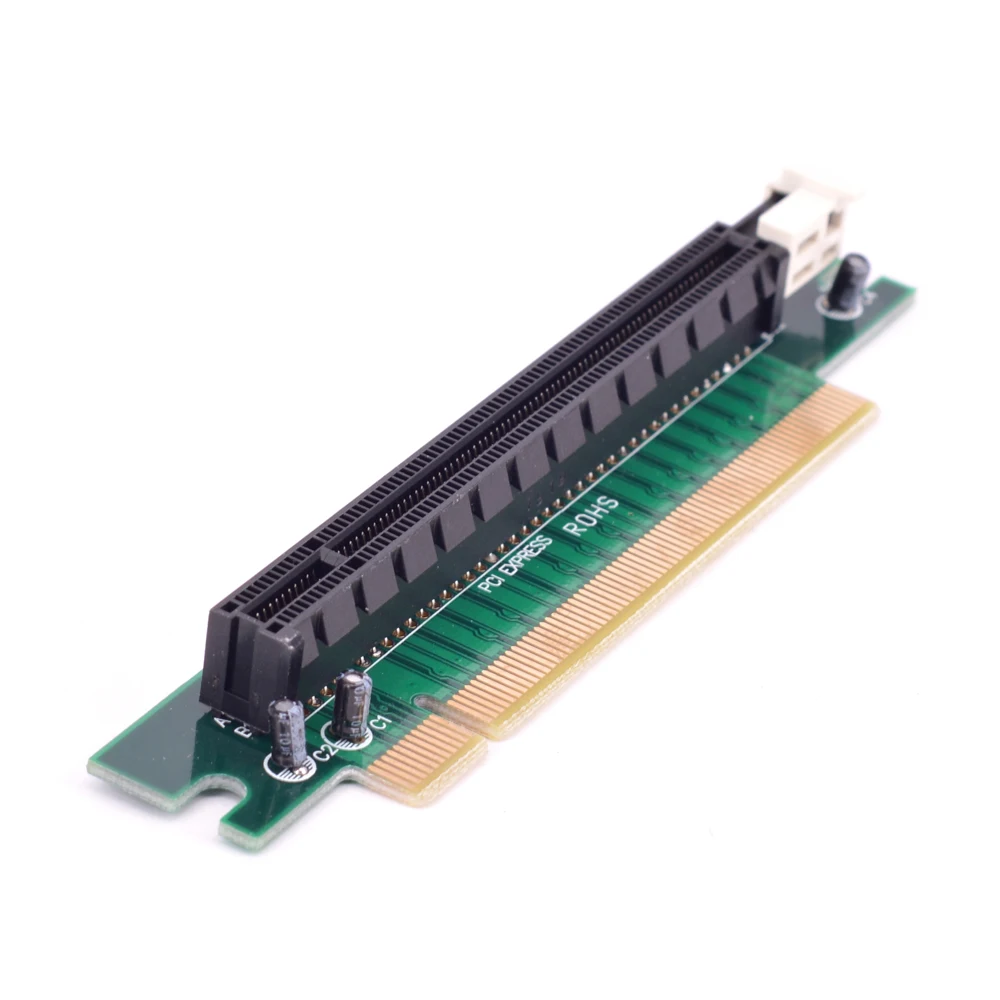

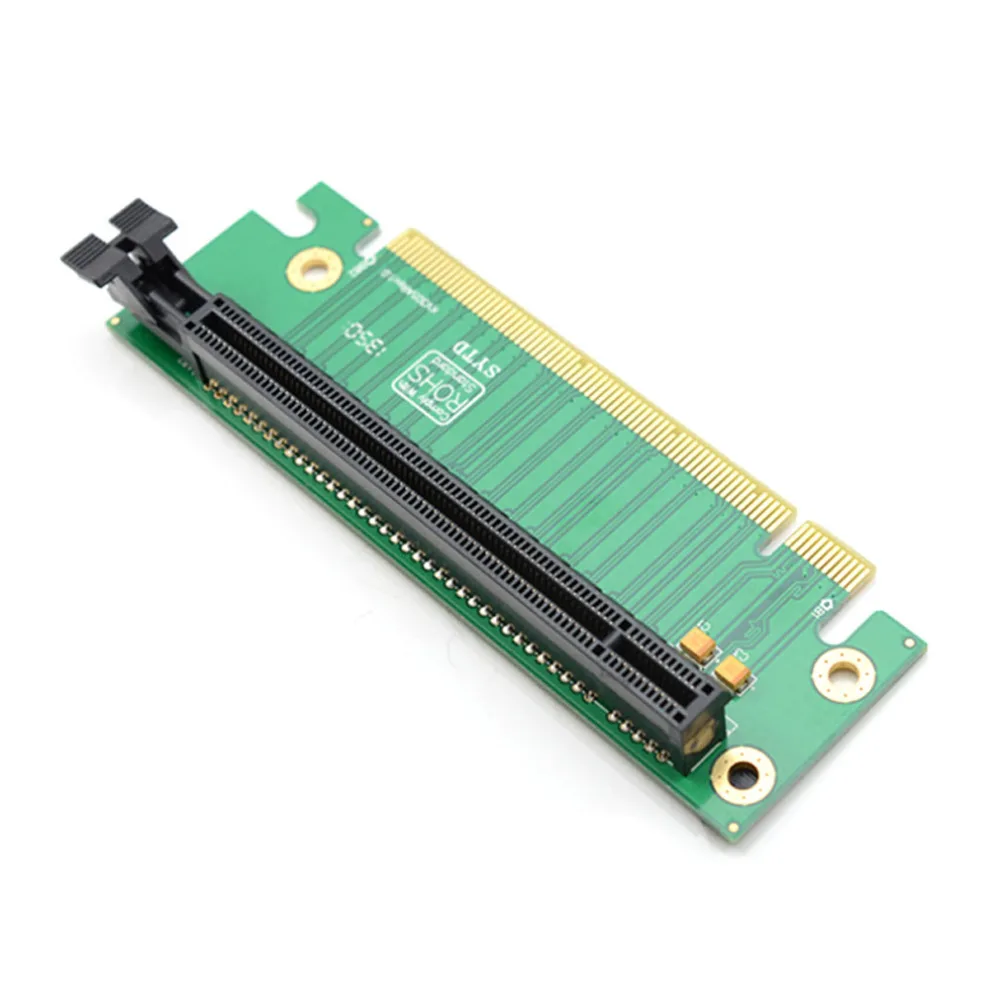

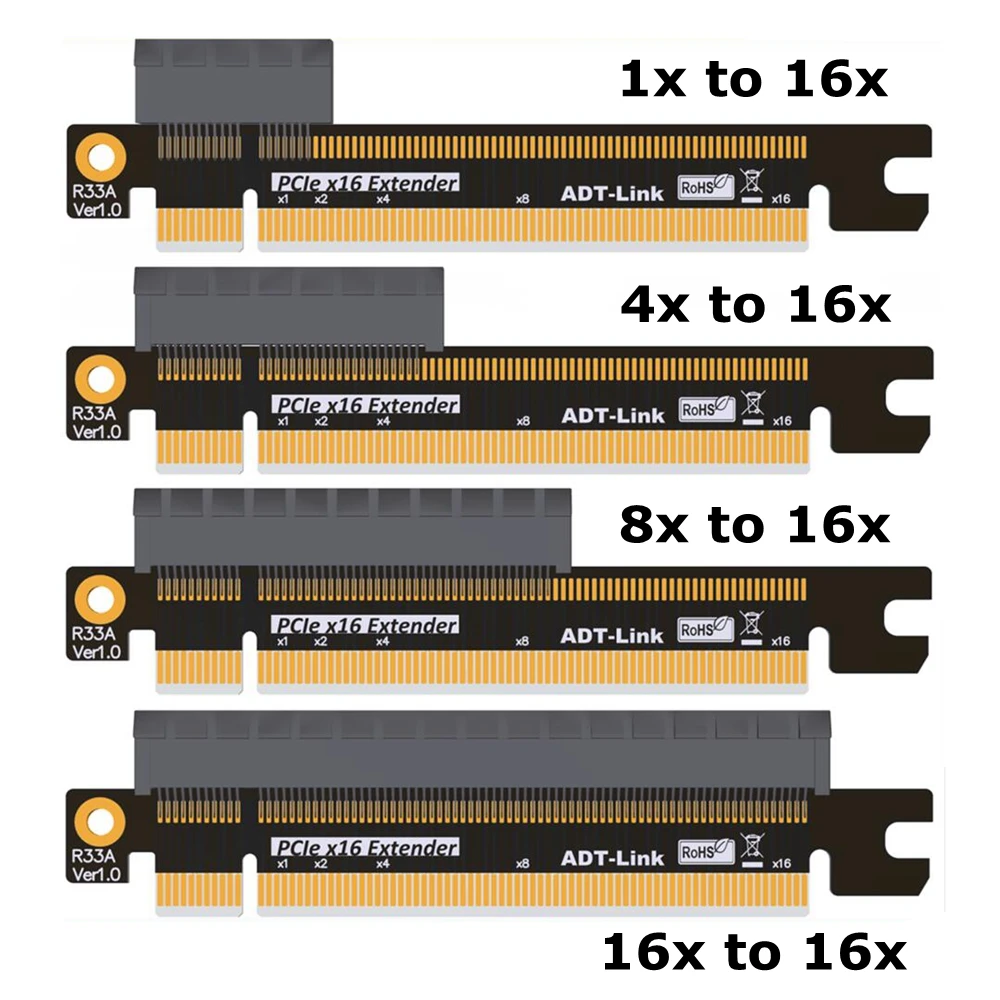

А если вы устанете от слота Mini PCI-e x1, вы сможете просто перейти на слот x16. Мне кажется, что при этом он работает, как x1, но имеет полный размер… Ну, потому что:

А вот плата с VGA, которая видеокарта. Она приспособлена для 86Duino, удобной встроенной системы x86, которую я всё никак не куплю:

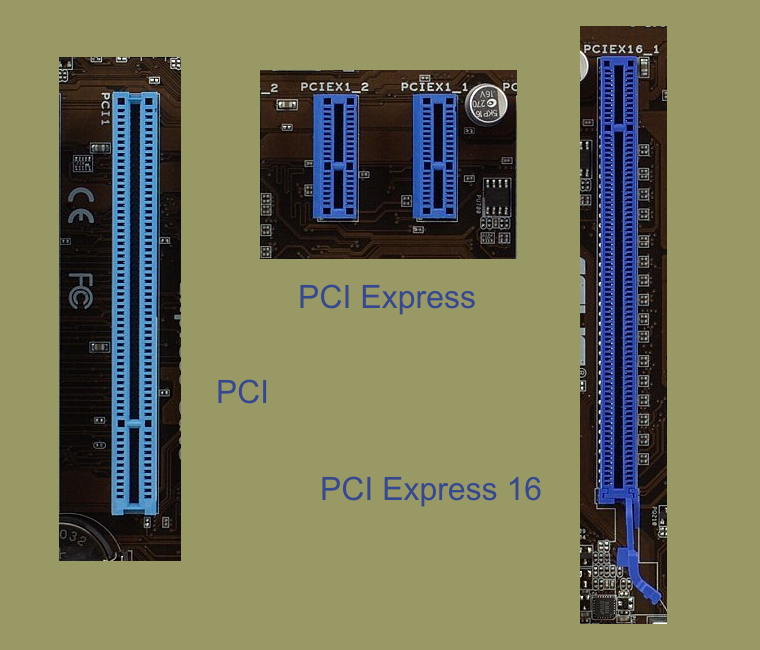

Как работает PCI Express | HowStuffWorks

Слоты Peripheral Component Interconnect (PCI) являются такой неотъемлемой частью архитектуры компьютера, что большинство людей воспринимает их как должное. В течение многих лет PCI был универсальным и функциональным способом подключения звуковых, видео и сетевых карт к материнской плате.

Но у PCI есть недостатки. Поскольку процессоры, видеокарты, звуковые карты и сети становятся быстрее и мощнее, PCI остается прежним.Он имеет фиксированную ширину 32 бита и может одновременно обрабатывать только 5 устройств. Более новая 64-битная шина PCI-X обеспечивает большую пропускную способность, но ее большая ширина усугубляет некоторые другие проблемы PCI.

Новый протокол под названием PCI Express (PCIe) устраняет многие из этих недостатков, обеспечивает большую пропускную способность и совместим с существующими операционными системами. В этой статье мы рассмотрим, чем PCIe отличается от PCI. Мы также рассмотрим, как PCI Express делает компьютер быстрее, потенциально может повысить производительность графики и заменить слот AGP.

Высокоскоростное последовательное соединение

На заре компьютерных технологий огромное количество данных передавалось по последовательным соединениям. Компьютеры разделяли данные на пакеты, а затем перемещали пакеты из одного места в другое по очереди. Последовательные соединения были надежными, но медленными, поэтому производители начали использовать параллельные соединения для одновременной отправки нескольких фрагментов данных.

Последовательные соединения были надежными, но медленными, поэтому производители начали использовать параллельные соединения для одновременной отправки нескольких фрагментов данных.

Оказывается, у параллельных подключений есть свои проблемы по мере того, как скорости становятся все выше и выше — например, провода могут электромагнитно мешать друг другу — так что теперь маятник качнулся обратно в сторону высокооптимизированных последовательных подключений.Усовершенствования оборудования и процесса разделения, маркировки и повторной сборки пакетов привели к гораздо более быстрым последовательным соединениям, таким как USB 2.0 и FireWire.

PCI Express — это последовательное соединение, которое больше похоже на сеть, чем на шину. Вместо одной шины, которая обрабатывает данные из нескольких источников, у PCIe есть переключатель, который управляет несколькими последовательными соединениями точка-точка. (Подробнее см. В разделе «Как работают коммутаторы LAN».) Эти соединения расходятся от коммутатора, ведущие непосредственно к устройствам, на которые должны передаваться данные. Каждое устройство имеет собственное выделенное соединение, поэтому устройства больше не разделяют пропускную способность, как на обычной шине. Мы посмотрим, как это происходит, в следующем разделе.

Каждое устройство имеет собственное выделенное соединение, поэтому устройства больше не разделяют пропускную способность, как на обычной шине. Мы посмотрим, как это происходит, в следующем разделе.

Разъемы и выводы блока питания

Лист данных стандартного разъема заголовка ATX с шагом 4,2 мм

ATX 24-контактный разъем основного кабеля питания

24-контактный основной разъем питания был добавлен в ATX12V 2.0 для обеспечения дополнительного питания, необходимого для слотов PCI Express.В старом 20-контактном основном кабеле питания есть только одна линия на 12 В. Новый 24-контактный разъем добавил по одной линии для заземления, 3,3, 5 и 12 вольт. Дополнительные контакты сделали дополнительный кабель питания ненужным, поэтому у большинства блоков питания ATX12V 2.x их нет. 24-контактный разъем поляризован, поэтому его можно вставлять только в правильном направлении.

| Распиновка | |||||

|---|---|---|---|---|---|

| Контакты с 1 по 12 | Контакты с 13 по 24 | ||||

| Описание | Цвет провода | Номер контакта | Номер контакта | Цвет провода | Описание |

+3. 3 вольта 3 вольта | оранжевый | 1 | 13 | оранжевый | +3,3 В |

| +3,3 В | оранжевый | 2 | 14 | синий | -12 вольт |

| земля | черный | 3 | 15 | черный | земля |

| +5 В | красный | 4 | 16 | зеленый | ПС_ОН № |

| земля | черный | 5 | 17 | черный | земля |

| +5 В | красный | 6 | 18 | черный | земля |

| земля | черный | 7 | 19 | черный | земля |

| PWR_OK | серый | 8 | 20 | белый | -5 вольт (опционально) |

| VSB +5 В | фиолетовый | 9 | 21 | красный | +5 вольт |

| +12 В | желтый | 10 | 22 | красный | +5 вольт |

| +12 В | желтый | 11 | 23 | красный | +5 вольт |

+3. 3 вольта 3 вольта | оранжевый | 12 | 24 | черный | земля |

Некоторые линии напряжения на соединителе могут иметь меньшие измерительные провода, которые позволяют источнику питания определять, какое напряжение на самом деле видит материнская плата. Они довольно часто встречаются на линии 3,3 В на выводе 13, но иногда используются и для других напряжений. Линия -5 В на выводе 20 была сделана необязательной в ATX12V 1.3 (введен в 2003 г.), потому что -5 годами редко использовался. Новые материнские платы практически никогда не требуют -5 вольт, в отличие от многих старых материнских плат. Большинство новых блоков питания не обеспечивают -5 вольт, и в этом случае белый провод отсутствует.

| Номера деталей разъема | |||

|---|---|---|---|

| Разъем материнской платы | |||

PCI — OSDev Wiki

Шина PCI

Шина PCI (Peripheral Component Interconnect) была определена для создания высокопроизводительной и недорогой локальной шины, которая останется в продуктах нескольких поколений. Благодаря сочетанию прозрачного пути обновления со 132 МБ / с (32-бит на 33 МГц) до 528 МБ / с (64-бит на 66 МГц) и сигнальных сред 5 В и 3,3 В шина PCI удовлетворяет потребности обоих недорогие настольные системы и высокопроизводительные серверы LAN. Компонент шины PCI и интерфейс платы расширения не зависят от процессора, что обеспечивает эффективный переход на будущие процессоры, а также возможность использования с несколькими архитектурами процессоров. Недостатком шины PCI является ограниченное количество электрических нагрузок, которыми она может управлять.Одна шина PCI может управлять максимум 10 нагрузками. (Помните, что при подсчете количества нагрузок на шине коннектор считается одной нагрузкой, а устройство PCI считается другой, а иногда и двумя.)

Благодаря сочетанию прозрачного пути обновления со 132 МБ / с (32-бит на 33 МГц) до 528 МБ / с (64-бит на 66 МГц) и сигнальных сред 5 В и 3,3 В шина PCI удовлетворяет потребности обоих недорогие настольные системы и высокопроизводительные серверы LAN. Компонент шины PCI и интерфейс платы расширения не зависят от процессора, что обеспечивает эффективный переход на будущие процессоры, а также возможность использования с несколькими архитектурами процессоров. Недостатком шины PCI является ограниченное количество электрических нагрузок, которыми она может управлять.Одна шина PCI может управлять максимум 10 нагрузками. (Помните, что при подсчете количества нагрузок на шине коннектор считается одной нагрузкой, а устройство PCI считается другой, а иногда и двумя.)

Пространство конфигурации

Спецификация PCI предусматривает полностью программную инициализацию и настройку каждого устройства (или цели) на шине PCI через отдельное адресное пространство конфигурации. Все устройства PCI, за исключением мостов главной шины, должны предоставлять для этой цели 256 байтов регистров конфигурации.

Циклы чтения / записи конфигурации используются для доступа к пространству конфигурации каждого целевого устройства. Цель выбирается во время доступа к конфигурации, когда заявлен ее сигнал IDSEL. IDSEL действует как классический сигнал выбора микросхемы. Во время фазы адресации цикла конфигурации процессор может адресовать один из 64 32-битных регистров в пространстве конфигурации, помещая требуемый номер регистра в адресные строки 2–7 (AD [7..2]) и строки разрешения байтов. .

Устройства PCI по своей природе имеют прямой порядок байтов, что означает, что все многобайтовые поля имеют наименее значимые значения по младшим адресам.Для этого требуется процессор с прямым порядком байтов, такой как Power PC, для выполнения правильной перестановки байтов данных, считываемых с устройства PCI или записываемых на него, включая любые обращения к адресному пространству конфигурации.

Системы должны обеспечивать механизм, позволяющий получить доступ к пространству конфигурации PCI, так как большинство ЦП не имеют такого механизма.

Механизм доступа к пространству конфигурации № 1

Используются два 32-битных местоположения ввода-вывода, первое местоположение (0xCF8) называется CONFIG_ADDRESS, а второе (0xCFC) называется CONFIG_DATA. CONFIG_ADDRESS указывает адрес конфигурации, к которому требуется доступ, в то время как доступ к CONFIG_DATA будет фактически генерировать доступ к конфигурации и будет передавать данные в регистр CONFIG_DATA или из него.

CONFIG_ADDRESS — это 32-битный регистр, формат которого показан на следующем рисунке. Бит 31 — это флаг разрешения для определения, когда доступ к CONFIG_DATA должен быть преобразован в циклы конфигурации. Биты с 23 по 16 позволяют программному обеспечению конфигурации выбрать конкретную шину PCI в системе. Биты с 15 по 11 выбирают конкретное устройство на шине PCI. Биты с 10 по 8 выбирают конкретную функцию в устройстве (если устройство поддерживает несколько функций).

Биты с 23 по 16 позволяют программному обеспечению конфигурации выбрать конкретную шину PCI в системе. Биты с 15 по 11 выбирают конкретное устройство на шине PCI. Биты с 10 по 8 выбирают конкретную функцию в устройстве (если устройство поддерживает несколько функций).

Младший байт выбирает смещение в 256-байтовом пространстве конфигурации, доступном с помощью этого метода.Поскольку все операции чтения и записи должны быть как 32-битными, так и выровненными для работы во всех реализациях, два младших бита CONFIG_ADDRESS всегда должны быть нулевыми, а оставшиеся шесть битов позволяют вам выбирать каждое из 64 32-битных слов. Если вам не нужны все 32 бита, вам придется выполнить невыровненный доступ в программном обеспечении, выровняв адрес с последующим маскированием и сдвигом ответа.

| 31 | 30–24 | 23–16 | 15–11 | 10–8 | 7-0 |

|---|---|---|---|---|---|

| Бит включения | Зарезервировано | Номер автобуса | Номер устройства | Номер функции | Смещение регистра¹ |

¹ Смещение регистра должно указывать на последовательные DWORD, т. е.биты 1: 0 всегда равны 0b00 (они все еще являются частью смещения регистра).

е.биты 1: 0 всегда равны 0b00 (они все еще являются частью смещения регистра).

Следующий сегмент кода иллюстрирует использование механизма конфигурации # 1 для чтения 16-битных полей из пространства конфигурации. Обратите внимание, что этот сегмент, функции outl (порт, значение) и inl (порт) относятся к инструкциям на языке ассемблера Pentium OUTL и INL.

uint16_t pciConfigReadWord (шина uint8_t, слот uint8_t, функция uint8_t, смещение uint8_t) {

адрес uint32_t;

uint32_t lbus = (uint32_t) шина;

uint32_t lslot = (uint32_t) слот;

uint32_t lfunc = (uint32_t) func;

uint16_t tmp = 0;

/ * создаем адрес конфигурации, как показано на рисунке 1 * /

адрес = (uint32_t) ((lbus << 16) | (lslot << 11) |

(lfunc << 8) | (смещение & 0xfc) | ((uint32_t) 0x80000000));

/ * выписываем адрес * /

outl (0xCF8, адрес);

/ * считываем данные * /

/ * (offset & 2) * 8) = 0 выберет первое слово 32-битного регистра * /

tmp = (uint16_t) ((inl (0xCFC) >> ((смещение & 2) * 8)) & 0xffff);

возврат (tmp);

} Когда при доступе к конфигурации делается попытка выбрать несуществующее устройство, хост-мост завершит доступ без ошибок, отбрасывая все данные при записи и возвращая все данные при чтении. Следующий сегмент кода иллюстрирует чтение несуществующего устройства.

uint16_t pciCheckVendor (шина uint8_t, слот uint8_t) {

uint16_t vendor, device;

/ * пытаемся прочитать первый регистр конфигурации. Поскольку нет * /

/ * поставщики, которые == 0xFFFF, это должно быть несуществующее устройство. * /

if ((vendor = pciConfigReadWord (bus, slot, 0,0))! = 0xFFFF) {

устройство = pciConfigReadWord (шина, слот, 0,2);

. . .

} return (поставщик);

} Механизм доступа к пространству конфигурации № 2

Этот механизм доступа к пространству конфигурации устарел в PCI версии 2.0. Это означает, что он, вероятно, будет существовать на оборудовании примерно с 1992 года (когда был представлен PCI 1.0) до 1993 года (когда был представлен PCI 2.0), что ограничивает его использование материнскими платами 80486 и ранними Pentium.

Для механизма доступа № 2 порт ввода-вывода по адресу 0x0CF8 является 8-битным портом и используется для включения / отключения механизма доступа и установки номера функции. Он имеет следующий формат:

Он имеет следующий формат:

| 7–4 | 3 — 1 | 0 |

|---|---|---|

| Ключ (0 = механизм доступа отключен, ненулевое значение = механизм доступа включен) | Номер функции | Специальный цикл разрешен, если установлен |

Порт ввода-вывода в 0x0CFA («регистр пересылки») также является 8-битным портом и используется для установки номера шины для последующих обращений к пространству конфигурации PCI.

После включения механизма доступа; доступы к портам ввода-вывода от 0xC000 до 0xCFFF используются для доступа к пространству конфигурации PCI. Номер порта ввода-вывода имеет следующий формат:

| 15–12 | 11–8 | 7–2 | 1 — 0 |

|---|---|---|---|

| Должно быть 1100b | Номер устройства | Регистровый индекс | Должен быть нулем |

Обратите внимание, что это ограничивает систему до 16 устройств на шину PCI.

Доступ к пространству конфигурации PCI с отображением памяти

PCI Express представил новый способ доступа к пространству конфигурации PCI, при котором просто отображается память и не используются порты ввода-вывода. Этот механизм доступа описан в PCI Express.

Обратите внимание, что системы, которые предоставляют механизм доступа с отображением памяти, также должны поддерживать механизм доступа PCI №1 для обратной совместимости.

Обнаружение механизма доступа к пространству конфигурации / с

В целом есть 4 корпуса:

- Компьютер не поддерживает PCI (либо компьютер слишком старый, либо ваша ОС запускается в будущем после замены PCI)

- компьютер поддерживает механизм №2

- компьютер поддерживает механизм №1, но не поддерживает механизм доступа с отображением памяти

- компьютер поддерживает как механизм №1, так и механизм доступа с отображением памяти

Для систем BIOS «int 0x1A, AX = 0xB101 (проверка наличия PCI BIOS)» сообщит вам, использует ли система механизм №1 или механизм №2. Если эта функция не существует, вы не можете быть уверены, поддерживает ли компьютер PCI или нет. Если он говорит, что механизм №1 поддерживается, вы не узнаете, поддерживается ли также механизм доступа с отображением памяти или нет.

Если эта функция не существует, вы не можете быть уверены, поддерживает ли компьютер PCI или нет. Если он говорит, что механизм №1 поддерживается, вы не узнаете, поддерживается ли также механизм доступа с отображением памяти или нет.

Для систем UEFI очень безопасно предположить, что механизм №2 не поддерживается; и вы можете проверить, поддерживает ли компьютер PCI или нет, проверив, существует ли протокол «Поддержка шины PCI». Если поддерживается PCI, нет простого способа определить, поддерживает ли (например) компьютер механизм №1 или нет.

Для систем BIOS и UEFI можно проверить таблицы ACPI, чтобы определить, поддерживается ли механизм доступа с отображением памяти.

Это оставляет несколько случаев невыясненными (например, когда вы не знаете, поддерживается ли механизм №1 или №2, несмотря на попытку всего вышеперечисленного). В этих случаях остается единственный вариант — зондирование вручную. Это означает 2 конкретных теста — поддерживается ли механизм №1 и если нет, поддерживается ли механизм №2. Обратите внимание, что ручное зондирование связано с риском; в том, что если нет PCI (т.е.г. в системе есть только ISA) доступ к порту ввода-вывода может вызвать неопределенное поведение (особенно в системах, где шина ISA игнорирует 6 старших бит адреса порта ввода-вывода, где доступ к порту ввода-вывода 0x0CF8 аналогичен доступу к порту ввода-вывода 0x00F8).

Обратите внимание, что ручное зондирование связано с риском; в том, что если нет PCI (т.е.г. в системе есть только ISA) доступ к порту ввода-вывода может вызвать неопределенное поведение (особенно в системах, где шина ISA игнорирует 6 старших бит адреса порта ввода-вывода, где доступ к порту ввода-вывода 0x0CF8 аналогичен доступу к порту ввода-вывода 0x00F8).

Структура устройства PCI

Спецификация PCI определяет организацию 256-байтовых регистров пространства конфигурации и вводит специальный шаблон для пространства. На рисунках 2 и 3 показана структура 256-байтового пространства конфигурации.Все совместимые с PCI устройства должны поддерживать поля Vendor ID, Device ID, Command and Status, Revision ID, Class Code и Header Type. Реализация других регистров не является обязательной, в зависимости от функциональности устройства.

Следующие описания полей являются общими для всех типов заголовков:

- ID устройства: Определяет конкретное устройство.

Если действительные идентификаторы назначаются поставщиком.

Если действительные идентификаторы назначаются поставщиком. - ID поставщика: Идентифицирует производителя устройства.Где допустимые идентификаторы выделяются PCI-SIG (список здесь) для обеспечения уникальности, а 0xFFFF — недопустимое значение, которое будет возвращено при доступе для чтения к регистрам пространства конфигурации несуществующих устройств.

- Состояние: Регистр, используемый для записи информации о состоянии для событий, связанных с шиной PCI.

- Команда: Обеспечивает контроль над способностью устройства генерировать циклы PCI и отвечать на них. Если единственная функция, которая гарантированно поддерживается всеми устройствами, — это когда в этот регистр записывается 0, устройство отключается от шины PCI для всех обращений, кроме доступа к пространству конфигурации.

- Код класса: Регистр только для чтения, указывающий тип функции, выполняемой устройством.

- Подкласс: Регистр только для чтения, который определяет конкретную функцию, которую выполняет устройство.

- Prog IF: Регистр только для чтения, который задает интерфейс программирования на уровне регистров, который есть у устройства, если он вообще есть.

- Идентификатор редакции: Задает идентификатор редакции для конкретного устройства. Если действительные идентификаторы назначаются поставщиком.

- BIST: Представляет это состояние и позволяет управлять устройством BIST (встроенное самотестирование).

- Тип заголовка: Определяет структуру остальной части заголовка, начиная с байта 0x10 заголовка, а также указывает, имеет ли устройство несколько функций. Если значение 0x00 определяет обычное устройство, значение 0x01 указывает мост PCI-to-PCI, а значение 0x02 указывает мост CardBus. Если бит 7 этого регистра установлен, устройство выполняет несколько функций; в противном случае это однофункциональное устройство.

- Таймер задержки: Задает таймер задержки в единицах тактовых импульсов шины PCI.

- Размер строки кэша: Задает размер строки системного кэша в 32-битных единицах.

Устройство может ограничить количество поддерживаемых размеров строки кэша. Если в это поле записано неподдерживаемое значение, устройство будет вести себя так, как если бы было записано значение 0.

Устройство может ограничить количество поддерживаемых размеров строки кэша. Если в это поле записано неподдерживаемое значение, устройство будет вести себя так, как если бы было записано значение 0.

Эта таблица применима, если Тип заголовка — 00h. (Фигура 2)

| регистр | смещение | бит 31-24 | бит 23-16 | бит 15-8 | бит 7-0 |

|---|---|---|---|---|---|

| 00 | 00 | ID устройства | ID поставщика | ||

| 01 | 04 | Статус | Команда | ||

| 02 | 08 | Код класса | Подкласс | Прог, IF | Идентификатор редакции |

| 03 | 0C | БИСТ | Тип заголовка | Таймер задержки | Размер строки кэша |

| 04 | 10 | Базовый адрес # 0 (BAR0) | |||

| 05 | 14 | Базовый адрес # 1 (BAR1) | |||

| 06 | 18 | Базовый адрес # 2 (BAR2) | |||

| 07 | 1С | Базовый адрес # 3 (BAR3) | |||

| 08 | 20 | Базовый адрес # 4 (BAR4) | |||

| 09 | 24 | Базовый адрес # 5 (BAR5) | |||

| 0A | 28 | Cardbus CIS Указатель | |||

| 0B | 2C | ID подсистемы | ID поставщика подсистемы | ||

| 0C | 30 | Базовый адрес ПЗУ расширения | |||

| 0D | 34 | Зарезервировано | Указатель возможностей | ||

| 0E | 38 | Зарезервировано | |||

| 0F | 3C | Максимальная задержка | мин Грант | PIN прерывания | линия прерывания |

Следующие описания полей применимы, если Тип заголовка равен 0x00:

- CardBus CIS Pointer: Указывает на структуру информации карты и используется устройствами, которые совместно используют микросхемы между CardBus и PCI.

- Линия прерывания: Определяет, к какому входу системных контроллеров прерываний подключен вывод прерывания устройства, и реализуется любым устройством, которое использует вывод прерывания. Для архитектуры x86 этот регистр соответствует номерам PIC IRQ 0-15 (а не номерам I / O APIC IRQ), а значение 0xFF не определяет соединение.

- Вывод прерывания: Указывает, какой вывод прерывания использует устройство. Где значение 0x01 — это INTA #, 0x02 — это INTB #, 0x03 — это INTC #, 0x04 — это INTD #, а 0x00 означает, что устройство не использует вывод прерывания.

- Макс. Задержка: Регистр только для чтения, который указывает, как часто устройству требуется доступ к шине PCI (в единицах 1/4 микросекунды).

- Min Grant: Регистр только для чтения, который указывает длину периода пакета в единицах 1/4 микросекунды, которая требуется устройству (при тактовой частоте 33 МГц).

- Указатель возможностей: точек (т.

Е. Смещение в пространстве конфигурации этой функции) к связанному списку новых возможностей, реализованных устройством.Используется, если бит 4 регистра состояния (бит списка возможностей) установлен в 1. Два нижних бита зарезервированы и должны быть замаскированы перед использованием указателя для доступа к пространству конфигурации.

Е. Смещение в пространстве конфигурации этой функции) к связанному списку новых возможностей, реализованных устройством.Используется, если бит 4 регистра состояния (бит списка возможностей) установлен в 1. Два нижних бита зарезервированы и должны быть замаскированы перед использованием указателя для доступа к пространству конфигурации.

Эта таблица применима, если тип заголовка — 01h (мост PCI-to-PCI) (рисунок 3)

| регистр | смещение | бит 31-24 | бит 23-16 | бит 15-8 | бит 7-0 |

|---|---|---|---|---|---|

| 00 | 00 | ID устройства | ID поставщика | ||

| 01 | 04 | Статус | Команда | ||

| 02 | 08 | Код класса | Подкласс | Прог, IF | Идентификатор редакции |

| 03 | 0C | БИСТ | Тип заголовка | Таймер задержки | Размер строки кэша |

| 04 | 10 | Базовый адрес # 0 (BAR0) | |||

| 05 | 14 | Базовый адрес # 1 (BAR1) | |||

| 06 | 18 | Вторичный таймер задержки | Номер подчиненной шины | Номер вторичной шины | Номер первичной шины |

| 07 | 1С | вторичный статус | Предел ввода / вывода | База ввода-вывода||

| 08 | 20 | Предел памяти | База памяти | ||

| 09 | 24 | Предел предварительно загружаемой памяти | База памяти с возможностью предварительной загрузки | ||

| 0A | 28 | Базовые верхние 32 бита с предварительной выборкой | |||

| 0B | 2C | Предел предварительной выборки, верхние 32 бита | |||

| 0C | 30 | Верхний предел ввода / вывода 16 бит | Верхние 16 бит базы ввода / вывода | ||

| 0D | 34 | Зарезервировано | Указатель возможностей | ||

| 0E | 38 | Базовый адрес ПЗУ расширения | |||

| 0F | 3C | Управление мостом | PIN прерывания | линия прерывания | |

Вот схема регистра типа заголовка:

| Бит 7 | Биты с 6 по 0 |

|---|---|

| MF | Тип заголовка |

- MF — Если MF = 1, то это устройство выполняет несколько функций.

- Тип заголовка — 00h Стандартный заголовок — 01h Мост PCI-to-PCI — 02h Мост CardBus

Регистр BIST

Вот схема регистра BIST:

| Бит 7 | Бит 6 | Биты 4 и 5 | Биты от 0 до 3 |

|---|---|---|---|

| Возможность BIST | Старт BIST | Зарезервировано | Код завершения |

- BIST Capable — вернет 1, устройство поддерживает BIST.

- Start BIST — Если установлено значение 1, запускается BIST. Этот бит сбрасывается после завершения BIST. Если BIST не завершается через 2 секунды, устройство должно выйти из строя из-за системного программного обеспечения.

- Код завершения — вернет 0 после выполнения BIST, если тест завершился успешно.

Эта таблица применима, если тип заголовка — 02h (мост PCI-to-CardBus)

| регистр | смещение | бит 31-24 | бит 23-16 | бит 15-8 | бит 7-0 |

|---|---|---|---|---|---|

| 00 | 00 | ID устройства | ID поставщика | ||

| 01 | 04 | Статус | Команда | ||

| 02 | 08 | Код класса | Подкласс | Прог, IF | Идентификатор редакции |

| 03 | 0C | БИСТ | Тип заголовка | Таймер задержки | Размер строки кэша |

| 04 | 10 | Базовый адрес CardBus Socket / ExCa | |||

| 05 | 14 | Дополнительный статус | Зарезервировано | Смещение списка возможностей | |

| 06 | 18 | Таймер задержки CardBus | Номер подчиненного автобуса | Номер автобуса CardBus | номер шины PCI |

| 07 | 1С | Базовый адрес памяти 0 | |||

| 08 | 20 | Предел памяти 0 | |||

| 09 | 24 | Базовый адрес памяти 1 | |||

| 0A | 28 | Предел памяти 1 | |||

| 0B | 2C | Базовый адрес ввода / вывода 0 | |||

| 0C | 30 | Предел ввода / вывода 0 | |||

| 0D | 34 | Базовый адрес ввода / вывода 1 | |||

| 0E | 38 | Предел ввода / вывода 1 | |||

| 0F | 3C | Управление мостом | PIN прерывания | линия прерывания | |

| 10 | 40 | ID поставщика подсистемы | ID устройства подсистемы | ||

| 11 | 44 | 16-битный базовый адрес устаревшей карты PC Card | |||

Регистр команд

Вот схема регистра команд:

| Биты с 11 по 15 | Бит 10 | Бит 9 | Бит 8 | Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| Зарезервировано | Отключение прерывания | Fast Back-to-Back Включить | SERR # Включить | Зарезервировано | Ответ об ошибке четности | Палитра VGA Snoop | Включение записи в память и недействительности | Специальные циклы | Bus Master | Объем памяти | Пространство ввода / вывода |

- Отключение прерывания — Если установлено значение 1, сигнал INTx # устройства отключен; в противном случае утверждение сигнала разрешено.

- Fast Back-Back Enable — Если установлено в 1, означает, что устройству разрешено генерировать быстрые обратные транзакции; в противном случае быстрые двусторонние транзакции разрешены только одному и тому же агенту.

- SERR # Enable — Если установлено в 1, драйвер SERR # включен; в противном случае драйвер отключен.

- Бит 7 — Начиная с версии 3.0 спецификации локальной шины PCI этот бит жестко привязан к 0. В более ранних версиях спецификации этот бит использовался устройствами и мог быть жестко привязан к 0, 1 или реализован как бит чтения / записи.

- Ответ об ошибке четности — Если установлено значение 1, устройство будет выполнять свои обычные действия при обнаружении ошибки четности; в противном случае при обнаружении ошибки устройство установит бит 15 регистра состояния (бит состояния обнаруженной ошибки четности), но не будет утверждать вывод PERR # (ошибка четности) и продолжит работу в обычном режиме.

- VGA Palette Snoop — Если установлено в 1, устройство не отвечает на записи в регистр палитры и будет отслеживать данные; в противном случае устройство будет обрабатывать доступ к записи палитры, как и все другие обращения.

- Разрешение записи и недействительности в память — Если установлено значение 1, устройство может генерировать команду «Запись в память и недействительность»; в противном случае необходимо использовать команду записи в память.

- Специальные циклы — Если установлено значение 1, устройство может контролировать операции специального цикла; в противном случае устройство их проигнорирует.

- Bus Master — Если установлено в 1, устройство может вести себя как мастер шины; в противном случае устройство не сможет генерировать доступ к PCI.

- Пространство памяти — Если установлено в 1, устройство может отвечать на доступы к пространству памяти; в противном случае ответ устройства отключен.

- Пространство ввода-вывода — Если установлено значение 1, устройство может отвечать на доступы к пространству ввода-вывода; в противном случае ответ устройства отключен.

Если ядро настраивает полосы BAR устройств, ядро также должно активировать биты 0 и 1 для его активации.

Регистр состояния

Вот схема регистра статуса:

| Бит 15 | Бит 14 | Бит 13 | Бит 12 | Бит 11 | Биты 9 и 10 | Бит 8 | Бит 7 | Бит 6 | Бит 5 | Бит 4 | Бит 3 | Биты от 0 до 2 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Обнаружена ошибка четности | Сигнализация системной ошибки | Получено прерывание ведущего | Получено прерывание цели | Сигнал прерывания цели | DEVSEL Timing | Ошибка четности основных данных | Возможность быстрого спина к спине | Зарезервировано | 66 МГц | Список возможностейСостояние прерывания | Зарезервировано |

- Обнаружена ошибка четности — этот бит будет установлен в 1 всякий раз, когда устройство обнаруживает ошибку четности, даже если обработка ошибок четности отключена.

- Сигнальная системная ошибка — Этот бит будет установлен в 1 всякий раз, когда устройство подтверждает номер SERR.

- Received Master Abort — Этот бит будет установлен в 1 ведущим устройством, когда его транзакция (за исключением транзакций специального цикла) завершается с помощью Master-Abort.

- Received Target Abort — Этот бит будет установлен в 1 ведущим устройством, когда его транзакция завершается с помощью Target-Abort.

- Сигнал прерывания цели — Этот бит будет установлен в 1 всякий раз, когда целевое устройство завершает транзакцию с помощью прерывания цели.

- DEVSEL Timing — Биты только для чтения, которые представляют самое медленное время, в течение которого устройство будет устанавливать DEVSEL # для любой команды шины, кроме чтения и записи пространства конфигурации. Где значение 0x00 представляет быструю синхронизацию, значение 0x01 представляет среднюю синхронизацию, а значение 0x02 представляет медленную синхронизацию.

- Ошибка четности основных данных — Этот бит устанавливается только при выполнении следующих условий. Агент шины подтвердил PERR # при чтении или наблюдал за подтверждением PERR # при записи, агент, устанавливающий бит, действовал как мастер шины для операции, в которой возникла ошибка, и бит 6 регистра команд (ответ на ошибку четности bit) установлен в 1.

- Fast Back-to-Back Capable — Если установлено 1, устройство может принимать быстрые двусторонние транзакции, которые исходят от другого агента; в противном случае транзакции могут быть приняты только от одного и того же агента.

- Бит 6 — Начиная с версии 3.0 спецификации локальной шины PCI, этот бит зарезервирован. В версии 2.1 спецификации этот бит использовался, чтобы указать, поддерживает ли устройство определяемые пользователем функции.

- 66 МГц Capable — Если установлено значение 1, устройство может работать на частоте 66 МГц; в противном случае устройство работает на частоте 33 МГц.

- Список возможностей — Если установлено значение 1, устройство реализует указатель для связанного списка новых возможностей со смещением 0x34; в противном случае связанный список будет недоступен.

- Состояние прерывания — Представляет состояние сигнала INTx # устройства. Если установлено в 1 и бит 10 регистра команд (бит запрета прерывания) установлен в 0, сигнал будет подтвержден; в противном случае сигнал будет проигнорирован.

Напомним, что устройства PCI следуют небольшому порядку ENDIAN.Нижние адреса содержат наименее значимые части поля. Программное обеспечение для управления этой структурой должно уделять особое внимание тому, чтобы порядок следования байтов следовал устройствам PCI, а не процессорам.

Регистры базового адреса

Регистры базового адреса (или BAR) могут использоваться для хранения адресов памяти, используемых устройством, или смещений для адресов портов. Как правило, полосы BAR адреса памяти должны располагаться в физической оперативной памяти, в то время как полосы BAR пространства ввода-вывода могут располагаться по любому адресу памяти (даже за пределами физической памяти). Чтобы различать их, вы можете проверить значение младшего бита. В следующих таблицах описаны два типа полос:

Чтобы различать их, вы можете проверить значение младшего бита. В следующих таблицах описаны два типа полос:

| 31 — 4 | 3 | 2 — 1 | 0 |

|---|---|---|---|

| 16-байтовый выровненный базовый адрес | с возможностью предварительной загрузки | Тип | Всегда 0 |

| 31 — 2 | 1 | 0 |

|---|---|---|

| 4-байтовый выровненный базовый адрес | Зарезервировано | Всегда 1 |

Поле «Тип» в структуре полосы памяти указывает размер базового регистра и место его отображения в памяти.Если он имеет значение 0x00, то базовый регистр имеет ширину 32 бита и может быть отображен в любом месте 32-битного пространства памяти. Значение 0x02 означает, что базовый регистр имеет ширину 64 бита и может быть отображен в любом месте 64-битного пространства памяти (64-битный регистр базового адреса потребляет 2 из доступных регистров базового адреса). Значение 0x01 зарезервировано с версии 3.0 Спецификации локальной шины PCI. В более ранних версиях он использовался для поддержки пространства памяти ниже 1 МБ (16-разрядный базовый регистр, который может быть отображен в любом месте 16-разрядного пространства памяти).

Значение 0x02 означает, что базовый регистр имеет ширину 64 бита и может быть отображен в любом месте 64-битного пространства памяти (64-битный регистр базового адреса потребляет 2 из доступных регистров базового адреса). Значение 0x01 зарезервировано с версии 3.0 Спецификации локальной шины PCI. В более ранних версиях он использовался для поддержки пространства памяти ниже 1 МБ (16-разрядный базовый регистр, который может быть отображен в любом месте 16-разрядного пространства памяти).

Если вы хотите получить фактический базовый адрес BAR, не забудьте замаскировать младшие биты. Для 16-битных полосок пространства памяти вы вычисляете (BAR [x] & 0xFFF0). Для 32-битных полосок пространства памяти вы вычисляете (BAR [x] & 0xFFFFFFF0). Для полос 64-битного пространства памяти вы вычисляете ((BAR [x] & 0xFFFFFFF0) + ((BAR [x + 1] & 0xFFFFFFFF) << 32)). Для полос ввода / вывода вы вычисляете (BAR [x] & 0xFFFFFFFC).

Чтобы определить объем адресного пространства, необходимого для устройства PCI, вы должны сохранить исходное значение BAR, записать значение всех единиц в регистр, а затем прочитать его обратно. Затем объем памяти можно определить путем маскирования информационных битов, выполнения побитового НЕ (‘~’ в C) и увеличения значения на 1. Затем следует восстановить исходное значение BAR. Регистр BAR выровнен естественным образом, и поэтому вы можете изменять только установленные биты. Например, если устройство использует 16 МБ, в нем будет BAR0, заполненный 0xFF000000 (0x01000000 после декодирования), и вы можете изменить только старшие 8 бит. [1]

Затем объем памяти можно определить путем маскирования информационных битов, выполнения побитового НЕ (‘~’ в C) и увеличения значения на 1. Затем следует восстановить исходное значение BAR. Регистр BAR выровнен естественным образом, и поэтому вы можете изменять только установленные биты. Например, если устройство использует 16 МБ, в нем будет BAR0, заполненный 0xFF000000 (0x01000000 после декодирования), и вы можете изменить только старшие 8 бит. [1]

Когда регистр базового адреса помечен как Prefetchable, это означает, что область не имеет побочных эффектов чтения (чтение из этого диапазона памяти не меняет никакого состояния), и процессору разрешено кэшировать загрузки из этой памяти региона и считывать его пакетами (обычно размер строки кэша).Аппаратному обеспечению также разрешено объединять повторяющиеся хранилища по одному и тому же адресу в одно хранилище самого последнего значения. Если вы используете разбиение по страницам и хотите максимальную производительность, вам следует сопоставить области MMIO с возможностью предварительной загрузки как WT (сквозная запись) вместо UC (некэшируемые). На x86 фрейм-буферы являются исключением, они почти всегда должны быть сопоставлены WC (запись-объединение).

На x86 фрейм-буферы являются исключением, они почти всегда должны быть сопоставлены WC (запись-объединение).

Регистры Class Code, Subclass и Prog IF используются для определения типа устройства, функции устройства и интерфейса программирования на уровне регистров, соответственно.

В следующей таблице подробно описаны большинство известных типов и функций устройств:

| Код класса | Подкласс | Прогр. IF |

|---|---|---|

| 0x00 — Несекретный | 0x00 — устройства, не поддерживающие VGA | — |

| 0x01 — VGA-совместимое устройство | — | |

| 0x01 — Контроллер запоминающего устройства | 0x00 — Контроллер шины SCSI | — |

| 0x01 — Контроллер IDE | 0x00 — контроллер, работающий только в режиме совместимости с ISA | |

| 0x05 — контроллер только в собственном режиме PCI | ||

| 0x0A — контроллер режима совместимости с ISA, поддерживает оба канала, переключенные в собственный режим PCI | ||

| 0x0F — контроллер собственного режима PCI, поддерживает оба канала, переключенные в режим совместимости с ISA | ||

| 0x80 — контроллер, работающий только в режиме совместимости с ISA, поддерживает управление шиной | ||

| 0x85 — контроллер только в собственном режиме PCI, поддерживает управление шиной | ||

| 0x8A — контроллер режима совместимости с ISA, поддерживает оба канала, переключенные в собственный режим PCI, поддерживает мастеринг шины | ||

| 0x8F — контроллер в собственном режиме PCI, поддерживает оба канала, переключенные в режим совместимости с ISA, поддерживает управление шиной | ||

| 0x02 — Контроллер гибких дисков | — | |

| 0x03 — Контроллер шины IPI | — | |

| 0x04 — RAID-контроллер | — | |

| 0x05 — Контроллер ATA | 0x20 — одиночный DMA | |

| 0x30 — связанный DMA | ||

| 0x06 — Последовательный ATA | 0x00 — интерфейс, зависящий от поставщика | |

0x01 — AHCI 1. 0 0 | ||

| 0x02 — последовательная шина хранения | ||

| 0x07 — SCSI с последовательным подключением | 0x00 — SAS | |

| 0x01 — последовательная шина хранения | ||

| 0x08 — Контроллер энергонезависимой памяти | 0x01 — NVMHCI | |

| 0x02 — NVM Express | ||

| 0x80 — Другое | — | |

| 0x02 — сетевой контроллер | 0x00 — Ethernet-контроллер | — |

| 0x01 — контроллер Token Ring | — | |

| 0x02 — Контроллер FDDI | — | |

| 0x03 — Контроллер банкомата | — | |

| 0x04 — Контроллер ISDN | — | |

| 0x05 — Контроллер WorldFip | — | |

| 0x06 — PICMG 2.14 Мультикомпьютер | — | |

| 0x07 — Контроллер Infiniband | — | |

| 0x08 — Контроллер ткани | — | |

| 0x80 — Другое | — | |

| 0x03 — Контроллер дисплея | 0x00 — VGA-совместимый контроллер | 0x00 — Контроллер VGA |

| 0x01 — 8514-совместимый контроллер | ||

| 0x01 — Контроллер XGA | — | |

| 0x02 — 3D-контроллер (не совместим с VGA) | — | |

| 0x80 — Другое | — | |

| 0x04 — Мультимедийный контроллер | 0x00 — Мультимедийный видеоконтроллер | — |

| 0x01 — Мультимедийный аудиоконтроллер | — | |

| 0x02 — Устройство компьютерной телефонии | — | |

| 0x03 — Аудиоустройство | — | |

| 0x80 — Другое | — | |

| 0x05 — Контроллер памяти | 0x00 — Контроллер ОЗУ | — |

| 0x01 — флэш-контроллер | — | |

| 0x80 — Другое | — | |

| 0x06 — Устройство моста | 0x00 — Хост-мост | — |

| 0x01 — мост ISA | — | |

| 0x02 — мост EISA | — | |

| 0x03 — Мост MCA | — | |

| 0x04 — мост PCI-to-PCI | 0x00 — нормальное декодирование | |

| 0x01 — Субтрактивное декодирование | ||

| 0x05 — Мост PCMCIA | — | |

| 0x06 — мост NuBus | — | |

| 0x07 — Мост CardBus | — | |

| 0x08 — Мост RACEway | 0x00 — прозрачный режим | |

| 0x01 — режим конечной точки | ||

| 0x09 — мост PCI-to-PCI | 0x40 — полупрозрачная, основная шина к центральному процессору | |

| 0x80 — полупрозрачный, вторичная шина к центральному процессору | ||

| 0x0A — Мост хоста InfiniBand-PCI | — | |

| 0x80 — Другое | — | |

| 0x07 — простой коммуникационный контроллер | 0x00 — последовательный контроллер | 0x00 — Совместимость с 8250 (Generic XT) |

| 0x01 — 16450-Совместимость | ||

| 0x02 — 16550-совместимый | ||

| 0x03 — 16650-Совместимость | ||

| 0x04 — 16750-Совместимость | ||

| 0x05 — 16850-Совместимость | ||

| 0x06 — 16950-Совместимость | ||

| 0x01 — параллельный контроллер | 0x00 — стандартный параллельный порт | |

| 0x01 — двунаправленный параллельный порт | ||

0x02 — ECP 1. X-совместимый параллельный порт X-совместимый параллельный порт | ||

| 0x03 — Контроллер IEEE 1284 | ||

| 0xFE — целевое устройство IEEE 1284 | ||

| 0x02 — Многопортовый последовательный контроллер | — | |

| 0x03 — Модем | 0x00 — Стандартный модем | |

| 0x01 — интерфейс, совместимый с Hayes 16450 | ||

| 0x02 — Интерфейс, совместимый с Hayes 16550 | ||

| 0x03 — Интерфейс, совместимый с Hayes 16650 | ||

| 0x04 — Интерфейс, совместимый с Hayes 16750 | ||

| 0x04 — IEEE 488.Контроллер 1/2 (GPIB) | — | |

| 0x05 — Смарт-карта | — | |

| 0x80 — Другое | — | |

| 0x08 — периферийное устройство базовой системы | 0x00 — ПИК | 0x00 — общий 8259-совместимый |

| 0x01 — Совместимость с ISA | ||

| 0x02 — Совместимость с EISA | ||

| 0x10 — Контроллер прерываний I / O APIC | ||

| 0x20 — I / O (x) Контроллер прерываний APIC | ||

| 0x01 — Контроллер DMA | 0x00 — общий 8237-совместимый | |

| 0x01 — Совместимость с ISA | ||

| 0x02 — Совместимость с EISA | ||

| 0x02 — Таймер | 0x00 — общий 8254-совместимый | |

| 0x01 — Совместимость с ISA | ||

| 0x02 — Совместимость с EISA | ||

| 0x03 — HPET | ||

| 0x03 — Контроллер RTC | 0x00 — общий RTC | |

| 0x01 — Совместимость с ISA | ||

| 0x04 — PCI контроллер горячей замены | — | |

| 0x05 — хост-контроллер SD | — | |

| 0x06 — IOMMU | — | |

| 0x80 — Другое | — | |

| 0x09 — Контроллер устройства ввода | 0x00 — Контроллер клавиатуры | — |

| 0x01 — цифровая ручка | — | |

| 0x02 — Контроллер мыши | — | |

| 0x03 — Контроллер сканера | — | |

| 0x04 — Контроллер игрового порта | 0x00 — общий | |

| 0x10 — Расширенный | ||

| 0x80 — Другое | — | |

| 0x0A — Док-станция | 0x00 — общий | — |

| 0x80 — Другое | — | |

| 0x0B — процессор | 0x00–386 | — |

| 0x01 — 486 | — | |

| 0x02 — Pentium | — | |

| 0x03 — Pentium Pro | — | |

| 0x10 — Альфа | — | |

| 0x20 — PowerPC | — | |

| 0x30 — MIPS | — | |

| 0x40 — сопроцессор | — | |

| 0x80 — Другое | — | |

| 0x0C — Контроллер последовательной шины | 0x00 — Контроллер FireWire (IEEE 1394) | 0x00 — общий |

| 0x10 — OHCI | ||

| 0x01 — Шина доступа | — | |

| 0x02 — SSA | — | |

| 0x03 — USB-контроллер | 0x00 — Контроллер UHCI | |

| 0x10 — Контроллер OHCI | ||

| 0x20 — Контроллер EHCI (USB2) | ||

| 0x30 — Контроллер XHCI (USB3) | ||

| 0x80 — Не указано | ||

| 0xFE — USB-устройство (не хост-контроллер) | ||

| 0x04 — Fibre Channel | — | |

| 0x05 — шина SMBus | — | |

| 0x06 — InfiniBand | — | |

| 0x07 — Интерфейс IPMI | 0x00 — СМИК | |

| 0x01 — Стиль контроллера клавиатуры | ||

| 0x02 — Передача блока | ||

| 0x08 — Интерфейс SERCOS (IEC 61491) | — | |

| 0x09 — CANbus | — | |

| 0x80 — Другое | — | |

| 0x0D — Беспроводной контроллер | 0x00 — совместимый контроллер iRDA | — |

| 0x01 — потребительский ИК-контроллер | — | |

| 0x10 — RF контроллер | — | |

| 0x11 — Контроллер Bluetooth | — | |

| 0x12 — широкополосный контроллер | — | |

0x20 — Ethernet-контроллер (802. 1а) 1а) | — | |

| 0x21 — Ethernet-контроллер (802.1b) | — | |

| 0x80 — Другое | — | |

| 0x0E — Интеллектуальный контроллер | 0x00 — I20 | — |

| 0x0F — Контроллер спутниковой связи | 0x01 — Контроллер спутникового ТВ | — |

| 0x02 — Контроллер спутникового аудио | — | |

| 0x03 — спутниковый голосовой контроллер | — | |

| 0x04 — спутниковый контроллер данных | — | |

| 0x10 — Контроллер шифрования | 0x00 — Сетевое и вычислительное шифрование / дешифрование | — |

| 0x10 — Шифрование / дешифрование развлечений | — | |

| 0x80 — Другое шифрование / дешифрование | — | |

| 0x11 — Контроллер обработки сигналов | 0x00 — Модули DPIO | — |

| 0x01 — Счетчики производительности | — | |

| 0x10 — Синхронизатор связи | — | |

| 0x20 — Управление обработкой сигналов | — | |

| 0x80 — Другое | — | |

| 0x12 — Ускоритель обработки | – | — |

| 0x13 — Неосновные приборы | – | — |

| 0x14 — 0x3F (Зарезервировано) | – | — |

| 0x40 — сопроцессор | – | — |

| 0x41 — 0xFE (Зарезервировано) | – | — |

| 0xFF — неназначенный класс (зависит от поставщика) | – | — |

Перечисление шин PCI

Существует 3 способа перечисления устройств на шинах PCI. Первый способ — это «грубая сила», проверка каждого устройства на каждой шине PCI (независимо от того, существует эта шина или нет). Второй способ позволяет избежать большого количества работы, выясняя действительные номера шины во время сканирования, и является немного более сложным, поскольку включает в себя рекурсию. Для обоих этих методов вы полагаетесь на что-то (прошивку) для правильной настройки шин PCI (настройка мостов PCI-PCI для пересылки запросов с одной шины на другую). Третий метод похож на второй, за исключением того, что вы настраиваете мосты PCI во время этого.

Первый способ — это «грубая сила», проверка каждого устройства на каждой шине PCI (независимо от того, существует эта шина или нет). Второй способ позволяет избежать большого количества работы, выясняя действительные номера шины во время сканирования, и является немного более сложным, поскольку включает в себя рекурсию. Для обоих этих методов вы полагаетесь на что-то (прошивку) для правильной настройки шин PCI (настройка мостов PCI-PCI для пересылки запросов с одной шины на другую). Третий метод похож на второй, за исключением того, что вы настраиваете мосты PCI во время этого.

Для всех трех методов вам необходимо иметь возможность проверить, присутствует ли конкретное устройство на определенной шине и является ли оно многофункциональным или нет. Псевдокод может выглядеть так:

void checkDevice (шина uint8_t, устройство uint8_t) {

uint8_t function = 0;

vendorID = getVendorID (шина, устройство, функция);

если (vendorID == 0xFFFF) возврат; // Устройство не существует

checkFunction (шина, устройство, функция);

headerType = getHeaderType (шина, устройство, функция);

if ((headerType & 0x80)! = 0) {

/ * Это многофункциональное устройство, поэтому проверьте оставшиеся функции * /

for (функция = 1; функция <8; функция ++) {

if (getVendorID (шина, устройство, функция)! = 0xFFFF) {

checkFunction (шина, устройство, функция);

}

}

}

}

void checkFunction (шина uint8_t, устройство uint8_t, функция uint8_t) {

} Обратите внимание, что если вы не проверяете бит 7 типа заголовка и не просматриваете все функции, то некоторые однофункциональные устройства будут сообщать подробности для «функции 0» для каждой функции.