Сравнение CISC и RISC архетиктур процессоров

Понятие

Оглавление

1.Описание CISC архитектуры.

2.Описания RISC архитектуры.

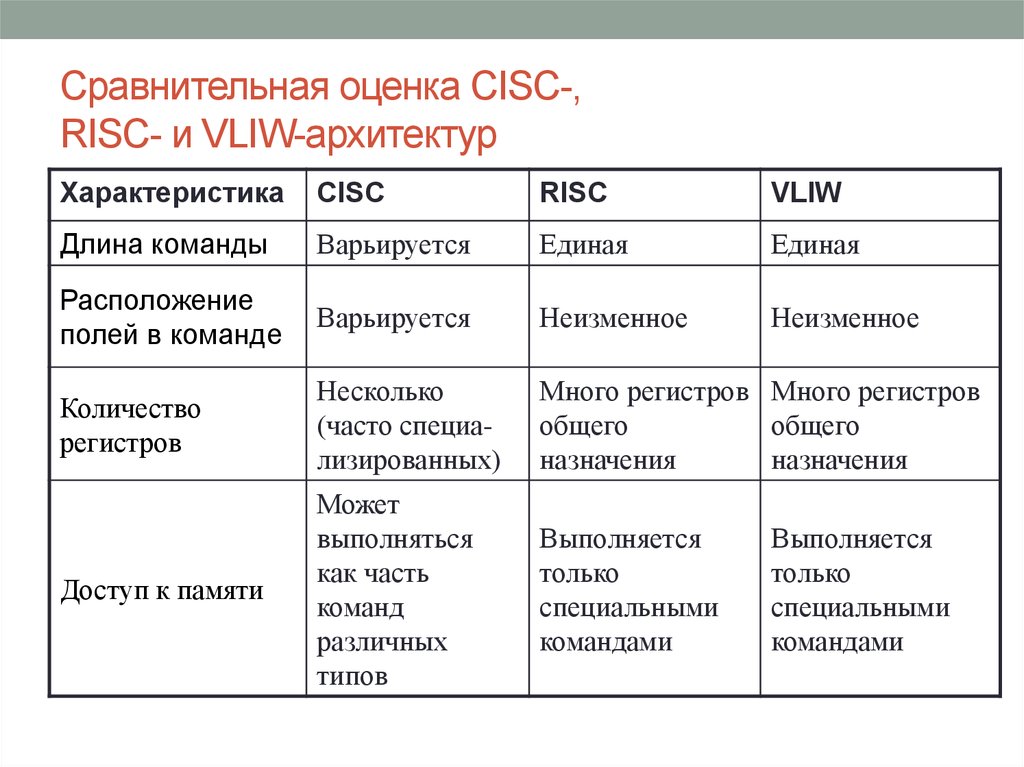

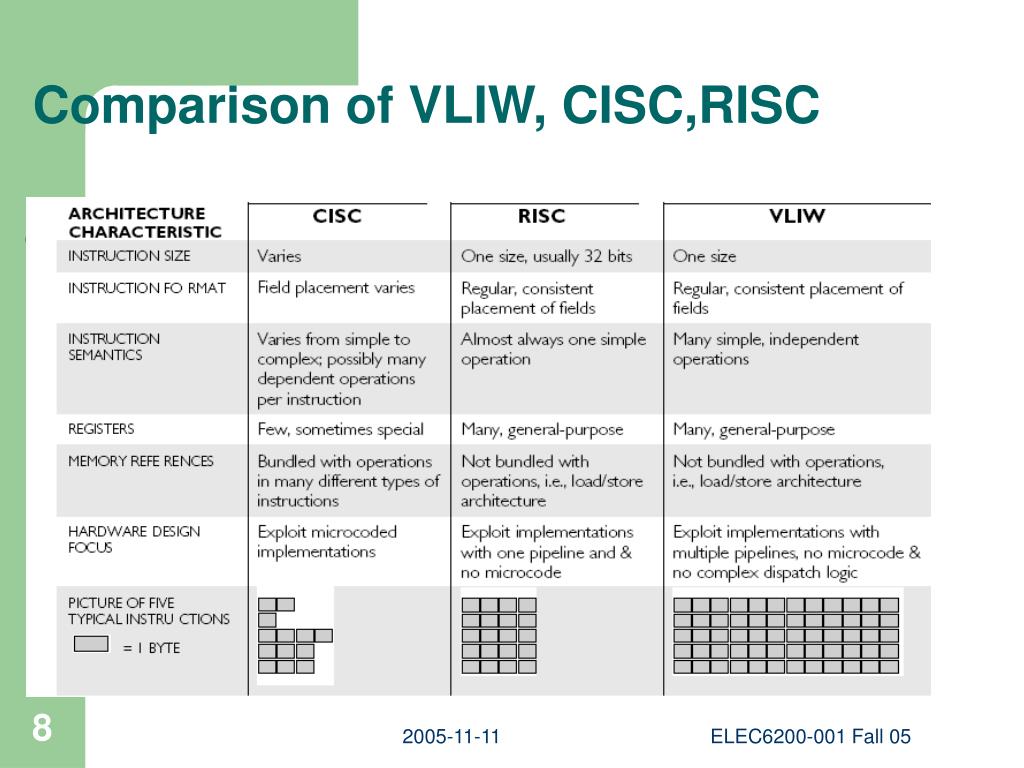

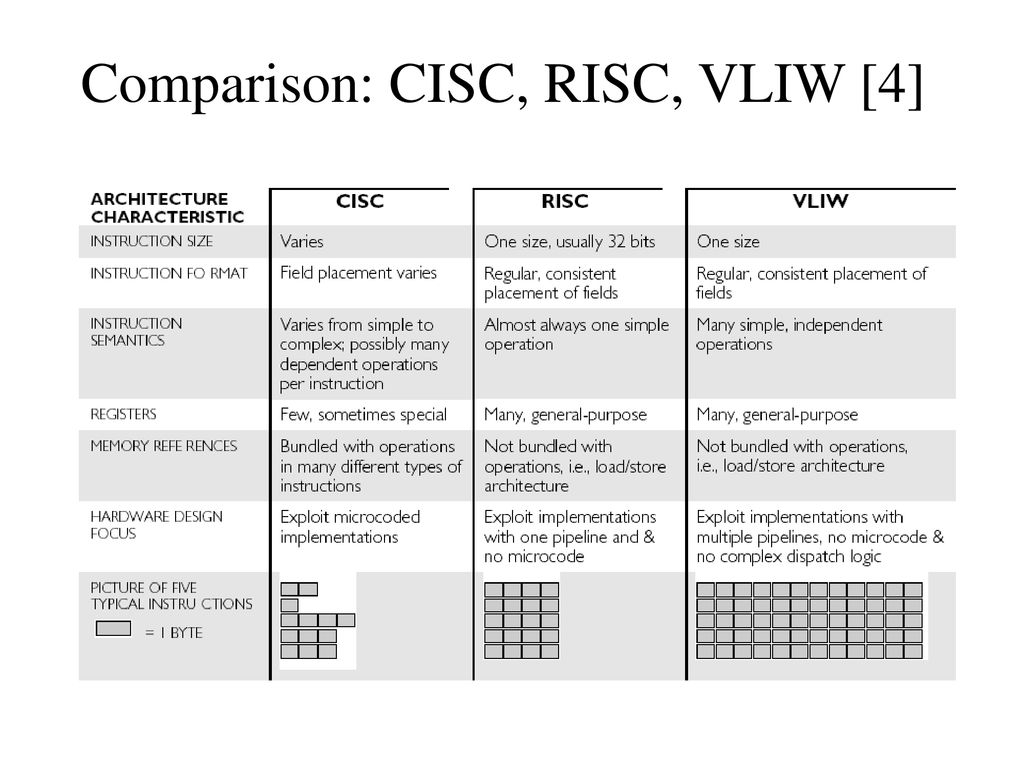

3.Сравнение CISC и RISC архитектур.

4.Понятие техпроцесса

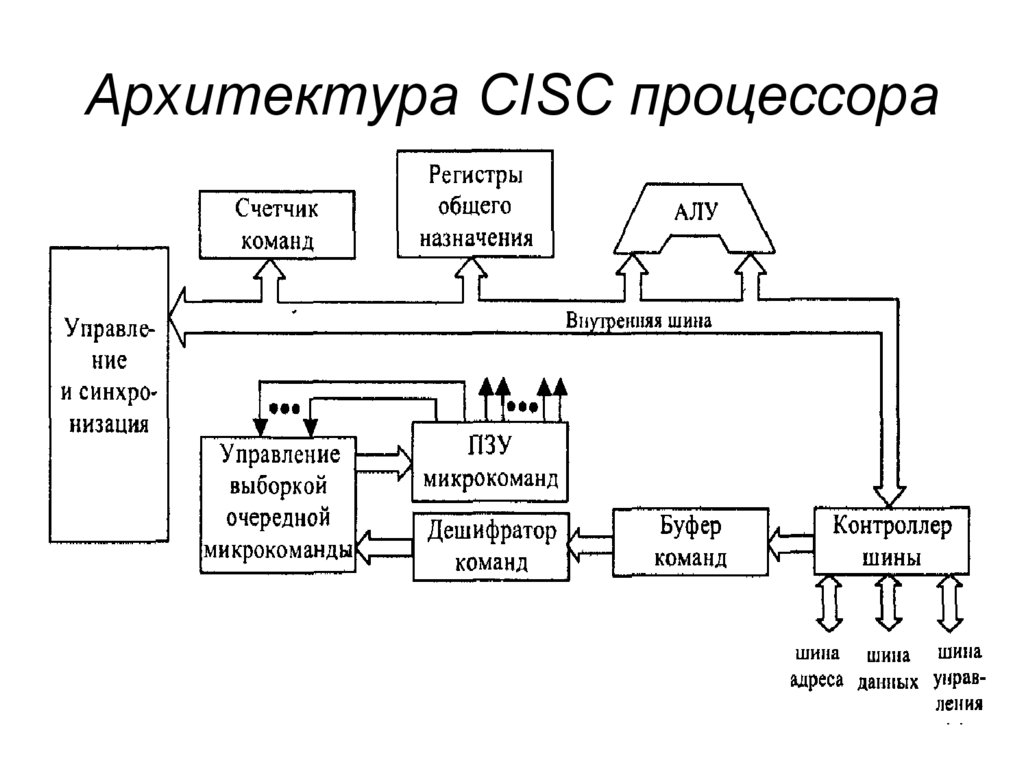

CISC

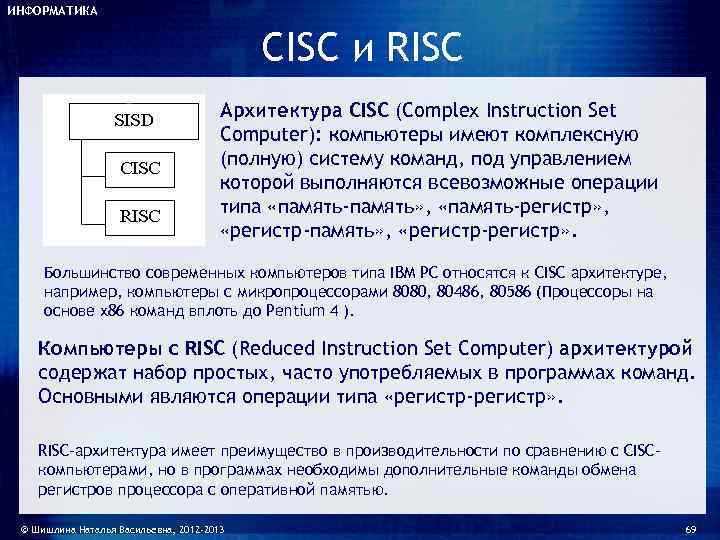

Исторически первые микропроцессоры, появившиеся в 70-х годах XX века, имели относительно простую систему команд, что объяснялось небольшими возможностями интегральной схемотехники. По мере увеличения степени интеграции разработчики МП старались расширять систему команд и делать команды более функциональными, «семантически нагруженными».

Это объяснялось, в частности, двумя моментами – во- первых, требованиями экономить память для размещения программ, оставлять больше памяти под данные и т.д., а во-вторых – возможностью реализовать внутри кристалла процессора сложные инструкции быстрее, чем при их программной реализации. В результате появились процессоры с большими наборами команд, причем команды эти также зачастую являлись достаточно сложными. В последствии эти МП назвали CISC.

CISC

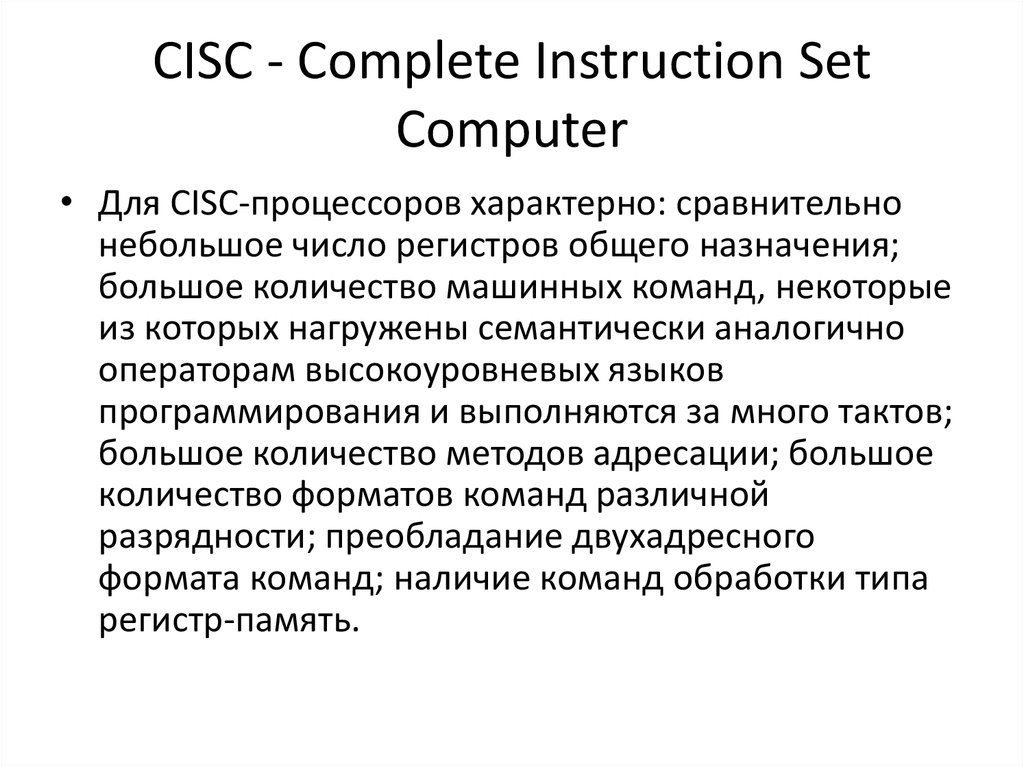

CISC ( Complex instruction set computing, или . complex instruction set computer —

компьютер с полным набором команд) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

●нефиксированное значение длины команды;

●арифметические действия кодируются в одной команде;

● небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Недостатки CISC

Наряду с отмеченными преимуществами процессоры CISC обладали и рядом недостатков, в частности – команды оказывались сильно неравнозначными по времени выполнения (разное количество тактов), плохо конвейеризовывались, требовали сложного (и длительного) декодирования и выполнения. Для повышения производительности стали использовать жесткую логику управления, что отразилось на регулярности и сложности кристаллов (нерегулярные кристаллы менее технологичны при изготовлении). На кристалле оставалось мало места для РОН и КЭШ.

История CISC

Типичными представителями являются большинство процессоров

семейства x86.

Например :

Intel 8008, Intel 80286, Motorola 68k

Что такое RISC?

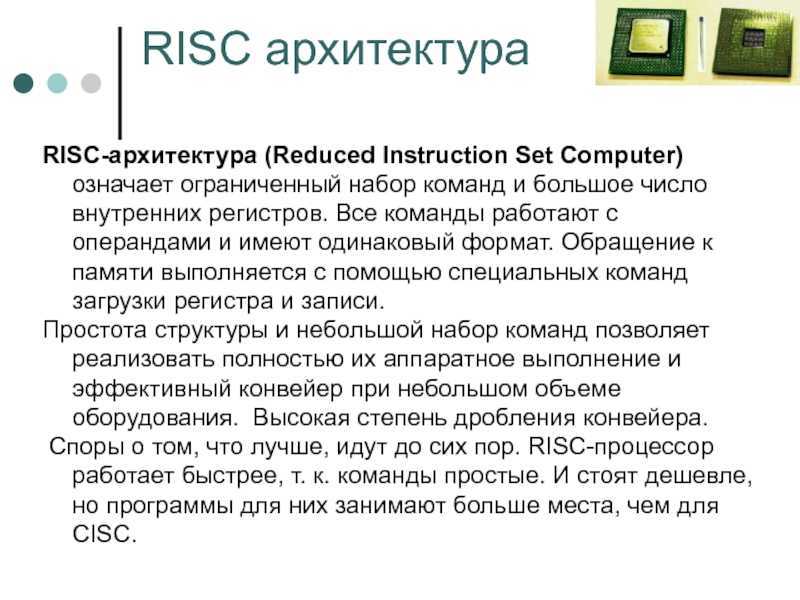

RISC (Reduced Instruction Set Computer) – архитектура процессора с сокращённым набором инструкций. Начало исследований в данной области положено компанией IBM в 1975 году. Правда фактически, RISC подобная архитектура была создана Сеймуром Крэйем в 1964 году и опробована в суперкомпьютере CDC 6600.

RISC

«Сокращённый набор команд» вовсе не означает, что процессор имеет малое количество инструкций. Это значит лишь то, что инструкции разделены на действия, результаты которых могут быть вычислены за определённый период времени (обычно один такт).

Особенности RISC

•1. Любая операция должна выполняться за один такт, вне зависимости от ее типа.

•2. Система команд должна содержать минимальное количество наиболее часто используемых простейших инструкций одинаковой длины.

•3. Операции обработки данных реализуются только в формате «регистр-регистр» (операнды выбираются из оперативных регистров

процессора, и результат операции записывается также в регистр; а обмен между оперативными регистрами и памятью выполняется только с помощью команд чтения/записи).

• 4. Состав системы команд должен быть «удобен» для компиляции операторов языков высокого уровня .

Обзоры

В разделе «Обзоры» представлены материалы, описывающие состояние различных сегментов рынка автоматизации в разные годы: исследования, статьи по истории автоматизации, описания новейших разработок и проектов, стенограммы мероприятий и много другой интересной и полезной информации.

- 2023 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2022 — (Журнал «СТА»)

- 2021 — (Журнал «СТА»)

- 2021 — (Журнал «СТА»)

- 2020 — (Журнал «СТА»)

- 2020 — (Журнал «СТА»)

- 2019 — (Журнал «СТА»)

- 2019 — (Журнал «СТА»)

- 2019 — (Журнал «СТА»)

- 2018 — (Журнал «СТА»)

- 2017 —

(

- 2017 —

(Портал Elec.

ru)

ru) - 2017 — (Издание PC Week/RE)

- 2017 — (Издание PC Week/RE)

- 2016 — (журнал «Алгоритм безопасности»)

- 2015 — (КИП «Индустрия & КИПиА»)

- 2014 — («Российская газета»)

- 2014 — (Газета «КоммерсантЪ»)

- 2014 — (Портал Минпромтог России)

- 2014 — (Портал Департамента радиоэлектронной промышленности Минпромторга)

- 2014 — (Журнал REM)

- 2014 — (Журнал «Эксперт»)

- 2014 — (Портал CRN)

- 2014 — (Портал «Управление производством»)

- 2013 — (www.pta-expo.ru)

- 2013 — (CONTROL ENGINEERING РОССИЯ, №3(45) 2013)

- 2013 — ( Gerald W. Cockrell CAP)

- 2013 — (Prepared by Piergiuseppe (Pino) Zani)

- 2013 —

- 2013 — (Nasledie.ru)

- 2013 — («Эксперт Урал» №8 (545))

- 2013 —

(www.

i-russia.ru)

i-russia.ru) - 2013 — (www.up-pro.ru)

- 2013 — (www.pta-expo.ru)

- 2012 — (www.Neftegaz.RU)

- 2012 — (www.pta-expo.ru)

- 2012 — (www.pta-expo.ru)

- 2012 — (Бизнес и класс, 2012)

- 2012 — (Рынок электротехники, сентябрь, 2012)

- 2012 — (Деловая Россия: промышленность, транспорт, социальная жизнь № 8 2012)

- 2012 — (Автоматизация и IT в энергетике, №7(36), июль 2012)

- 2012 — (КИПИНФО, №9 июнь 2012)

- 2012 —

(CONTROL ENGINEERING РОССИЯ, июнь 2012

- 2012 — (Автоматизация в промышленности, май 2012)

- 2012 — (www.pta-expo.ru)

- 2012 — (ЭЛЕКТРОНИКА НТБ 2(00116) 2012)

- 2012 — (Промышленные страницы Сибири № 3(62) апрель 2012)

- 2012 — (СТА №2/2012)

- 2012 —

(www.

pta-expo.ru)

pta-expo.ru) - 2012 — (CONTROL ENGINEERING РОССИЯ №4/2012)

- 2012 — (www.energypolis.ru)

- 2012 — (www.pta-expo.ru)

- 2012 — (www.i-smarthouse.ru)

- 2012 — (www.pta-expo.ru)

- 2011 — (www.pta-expo.ru)

- 2011 — (www.pta-expo.ru)

- 2011 — (www.up-pro.ru)

- 2011 — (www.dkvartal.ru)

- 2011 — (www.expert-ural.com )

- 2010 — (www.up-pro.ru)

- 2010 — (Профессиональный журнал, №4(76))

- 2010 — (www.cnews.ru)

- 2010 — (www.pta-expo.ru)

- 2010 — (www.pta-expo.ru)

- 2008 — (ИСУП, №4(20))

- 2008 — (www.pcweek.ru)

- 2008 — (www.pta-expo.ru)

- 2008 — (www.ingener.info)

- 2008 — (www.yokogawa.ru)

- 2007 —

(www.

ingener.info)

ingener.info) - 2007 — (www.ingener.info)

- 2001 —

- 2001 — (www.pcweek.ru)

- 1994 — (www.mka.ru)

- 1993 — (www.kommersant.ru)

- — (Журнал Control Engineering Russia)

Мы нацелены на развитие проекта, очень мобильны и открыты для сотрудничества

Если Вы располагаете интересными материалами, соответствующими концепции проекта,

присылайте их по адресу: [email protected]

или свяжитесь с нами по телефону: +7 (495) 234 22 10.

Авторские права строго соблюдаются.

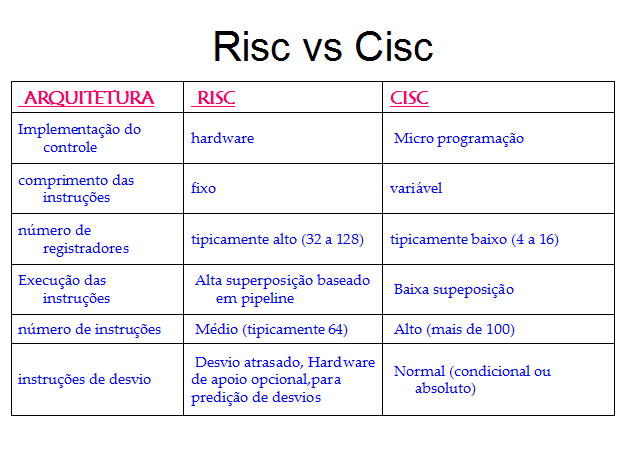

RISC и CISC: 20 ключевых сравнений

RISC и CISC представляют ключевые процессорные архитектуры, разработанные для повышения производительности ЦП.

- RISC и CISC — это популярные архитектуры процессоров, которые используют разные наборы инструкций по обработке данных для выполнения основных логических операций и операций ввода-вывода.

- В этой статье подробно рассматриваются архитектуры процессоров RISC и CISC, а также приводится их основное сравнение.

Содержание

- Что такое CISC?

- Что такое RISC?

- CISC и RISC: 20 ключевых сравнений

RISC (компьютер с сокращенным набором команд) и CISC (компьютер со сложным набором команд) относятся к популярным архитектурам процессоров, которые используют различные наборы инструкций по обработке данных для выполнения основных логических операций и операций ввода-вывода. У каждой архитектуры есть свой набор плюсов и минусов.

Прежде чем мы перейдем к архитектуре процессора, давайте сначала разберемся с рабочим процессом типичного процессора.

Процессоры или микроконтроллеры используют «наборы инструкций» для выполнения различных задач. Рассмотрим аналогию. Скажем, вы обучаете своего питомца понимать определенные команды, такие как «спать» и «бегать», которые связаны с конкретными задачами сна и бега. Позже, когда вы бросаете игрушку и даете своему питомцу команду «бежать», он бежит и приносит игрушку для вас.

Позже, когда вы бросаете игрушку и даете своему питомцу команду «бежать», он бежит и приносит игрушку для вас.

Типичный центральный процессор (ЦП), мозг компьютера, работает аналогичным образом, при этом ЦП приравнивается к процессорам и микроконтроллерам. Как и в приведенном выше примере, мы даем инструкции ЦП, который запускает транзисторы для включения и выключения для выполнения указанных инструкций.

Мы вводим инструкции в виде кодов операций или опкодов, которые выражаются в форме 0 и 1. Поскольку людям трудно запоминать и использовать комбинации нулей и единиц, мы используем понятные человеку инструкции. Эти инструкции представлены на языке ассемблера, который далее преобразуется компиляторами в понятные для машин коды операций 0 и 1.

Совокупность всех таких инструкций образует «набор инструкций». Это важный компонент любой вычислительной системы, поскольку от него зависит разработка нескольких языков высокого уровня, таких как Python, C# и других. Кроме того, дизайн аппаратного обеспечения и наборов инструкций используется в качестве метрики для оценки вычислительной скорости и производительности ЦП.

Производительность процессора определяется на основе количества программ, которые он может запустить за заданный промежуток времени. Математически это представляется как:

Производительность ЦП = Время/Программа = Инструкции/Программа X Циклы/Инструкции X Время/Цикл ….. [Уравнение 1]

Согласно этому уравнению, производительность ЦП зависит от количества инструкции в компьютерной программе. Это означает, что чем больше инструкций, тем больше времени требуется для их выполнения. В дальнейшем его можно упростить до количества тактов на инструкцию и времени на цикл.

Таким образом, производительность процессора можно оптимизировать двумя способами:

- Уменьшить количество инструкций на программу или

- Минимизировать количество циклов на инструкцию.

Поскольку эти два варианта дополняют друг друга, одновременное достижение обоих невозможно. Это означает, что улучшение одного параметра может легко пожертвовать другим. Однако все это только на поверхностном уровне; настоящие оптимизации, которые мы собираемся внедрить, глубоко укоренились в аппаратном обеспечении и наборе команд ЦП.

Однако все это только на поверхностном уровне; настоящие оптимизации, которые мы собираемся внедрить, глубоко укоренились в аппаратном обеспечении и наборе команд ЦП.

Основной целью архитектур RISC и CISC является повышение производительности процессора. Фундаментальное различие между ними заключается в том, что RISC имеет меньшее количество инструкций, каждая из которых способна выполнять одну операцию, в то время как CISC имеет большое количество сложных инструкций, способных выполнять несколько внутренних операций.

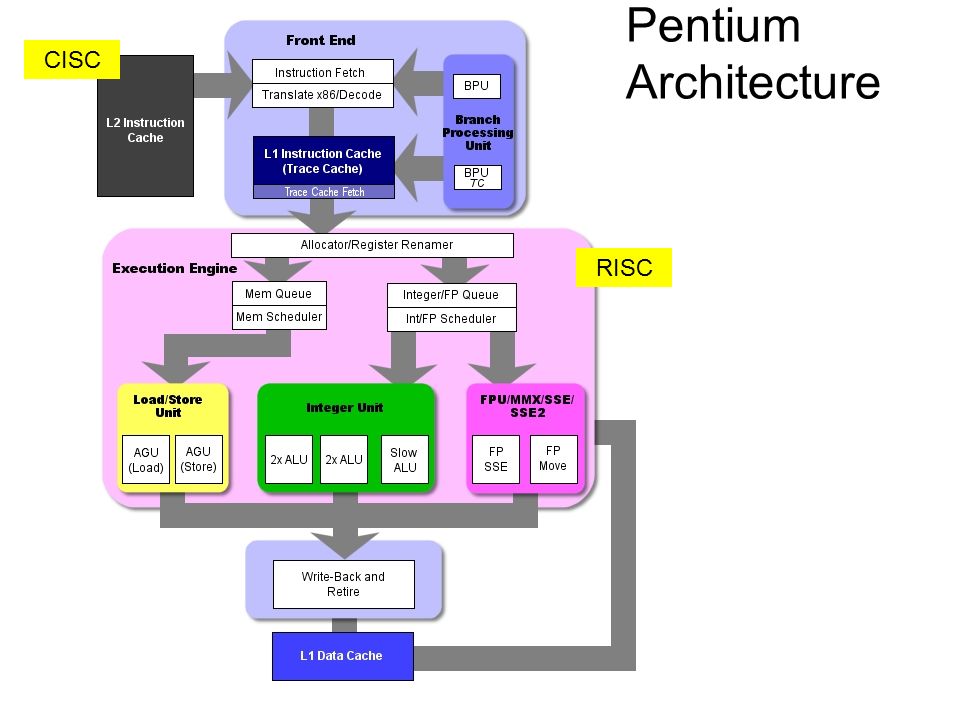

В индустрию процессоров входят компании, поддерживающие любую из двух архитектур. Например, машины Intel используют ЦП, работающие на архитектуре CISC, а ЦП Apple и машины ARM поставляются с процессорами и микроконтроллерами на основе RISC.

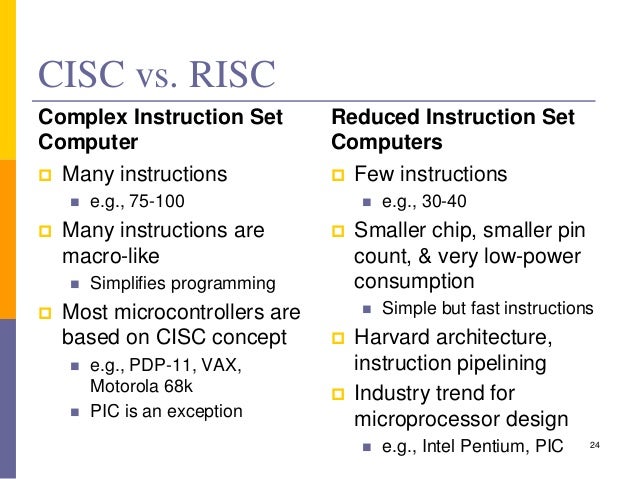

Что такое CISC?

CISC расшифровывается как «Complex Instruction Set Computer». Эта архитектура была представлена в 1970-х годах корпорацией Intel, когда самые ранние компьютеры были ориентированы на повышение скорости процессора за счет минимизации количества инструкций на программу (согласно уравнению 1). Эта цель была достигнута путем объединения нескольких простых команд в одну сложную инструкцию.

Эта цель была достигнута путем объединения нескольких простых команд в одну сложную инструкцию.

В аналогии с домашним животным команду «выполнить» можно назвать инструкцией CISC. Когда вы приказываете своему питомцу бежать, он выполняет ряд инструкций, таких как «отследить игрушку», затем «поднять игрушку», затем «вернуться к владельцу» и, наконец, «передать игрушку хозяину». Как показывает пример, гораздо удобнее и быстрее дать вашему питомцу одну команду «бежать», чем давать ему четыре независимых команды. Именно поэтому технологические компании, такие как Intel, предпочитали разрабатывать процессоры CISC в первые годы вычислений.

Давайте разберемся с этим с помощью простой инструкции CISC ADD, которая требует двух входных данных:

- Ячейки памяти двух чисел, необходимые для сложения

- Выполнить сложение и сохранить результат в первой ячейке памяти

| ADD 1800, 1801

Команда ADD берет числа из ячеек памяти 1800 и 1801 или регистров. Позже подобранные номера добавляются и в конечном итоге сохраняются в ячейке 1800.

Позже подобранные номера добавляются и в конечном итоге сохраняются в ячейке 1800.

Здесь одна инструкция ADD выполняет несколько низкоуровневых операций, таких как загрузка чисел из памяти, выполнение арифметической операции ADD и последующее сохранение результата в другой памяти. Рабочая нагрузка компилятора здесь значительно снижается, поскольку высокоуровневые инструкции легко вычисляются и сохраняются. Более того, эти инструкции потребляют минимум оперативной памяти, поскольку аппаратное обеспечение выполняет большинство задач при декодировании инструкций на начальных этапах.

Следовательно, в архитектурах CISC ЦП имеет право выполнять больше работы для выполнения одной инструкции. Поскольку выполнение инструкции занимает больше времени, тактовые частоты скомпрометированы. Кроме того, для операций CISC требуется больше транзисторов для декодирования сложных инструкций.

Наиболее известными примерами процессоров CISC являются AMD, Intel x86, VAX и System/360.

Подробнее: 10 лучших сетевых маршрутизаторов Mesh в 2022 году

Что такое RISC?

RISC означает «Компьютер с сокращенным набором инструкций». Они были введены в 1980-х годах Дэвидом Паттерсоном и Джоном Хеннесси для преодоления сложности процессоров CISC. Процессоры RISC работают с большим количеством инструкций; однако количество циклов, которое может потребоваться для выполнения инструкции, сведено к минимуму. В общих чертах, RISC-машине требуется один цикл ЦП для выполнения одной инструкции. Это может быть приравнено к инструкции «заснуть», которую вы дали своему обученному питомцу.

Давайте рассмотрим ту же инструкцию ADD и посмотрим, как ее выполняют устройства RISC. Начнем с того, что машины RISC не выполняют инструкцию ADD за один шаг. Вместо этого он разбит на несколько шагов. Например, вам нужно загрузить числа из памяти с помощью инструкции LOAD, за которой следует инструкция ADD, которая добавляет их, и, наконец, инструкция STORE, которая сохраняет результат в памяти.

| Нагрузка X, 1600

| Нагрузка Y, 1601

| ДОБАВИТЬ X, Y

| Сохранить 1600, X

В этом примере инструкция «Загрузить» загружает данные в ячейку памяти 1600 в регистр X. Точно так же вторая инструкция «Загрузить» берет данные из ячейки 1601 и загружает их в регистр Y. Позже значения в регистрах X и Y добавляются. Наконец, результат X сложения сохраняется в ячейке памяти 1600 или в любой другой ячейке. Стоит отметить, что операции в процессорах RISC-типа выполняются с «регистрами», а не непосредственно с памятью.

Хотя процесс кажется сложным, поскольку каждая из этих инструкций требует только одного такта, вся операция сложения выполняется за гораздо меньшее количество тактов. Однако такие временные преимущества также имеют некоторые недостатки. Например, поскольку процессоры RISC используют более простые наборы инструкций, сложные и высокоуровневые инструкции необходимо разделить на несколько простых инструкций.

Задача разбиения сложных команд на более простые тривиальна и выполняется компиляторами. В результате программные компоненты выполняют больше работы в RISC, чем аппаратное обеспечение процессора, как видно в CISC. Это возлагает дополнительную ответственность на разработчиков программного обеспечения, поскольку они несут ответственность в случае сбоя компилятора.

В отличие от процессоров CISC, логика машин RISC легко декодируется. Следовательно, для выполнения задач требуется меньше транзисторов. Архитектура RISC использует упрощенный набор инструкций, которые обычно работают меньше, но выполняются со значительной скоростью. Ключевая особенность таких машин заключается в том, что они позволяют разработчикам вписываться в более общие регистры ЦП и тем самым сосредоточиться на использовании параллельных потоков для выполнения сложных, но оптимизированных инструкций. Это повышает внутренний параллелизм и ускоряет время выполнения инструкций ЦП.

ARM (Advanced RISC Machine) — хорошо известный пример RISC-фреймворка. Это архитектура, разработанная компанией Arm Ltd. и основанная на принципах проектирования RISC. Его процессоры используются в настольных компьютерах, ноутбуках, смартфонах, игровых консолях и некоторых других интеллектуальных устройствах IoT, работающих от батареи, где важна энергоэффективность.

Это архитектура, разработанная компанией Arm Ltd. и основанная на принципах проектирования RISC. Его процессоры используются в настольных компьютерах, ноутбуках, смартфонах, игровых консолях и некоторых других интеллектуальных устройствах IoT, работающих от батареи, где важна энергоэффективность.

Подробнее: 10 лучших приложений IoT в 2022 году

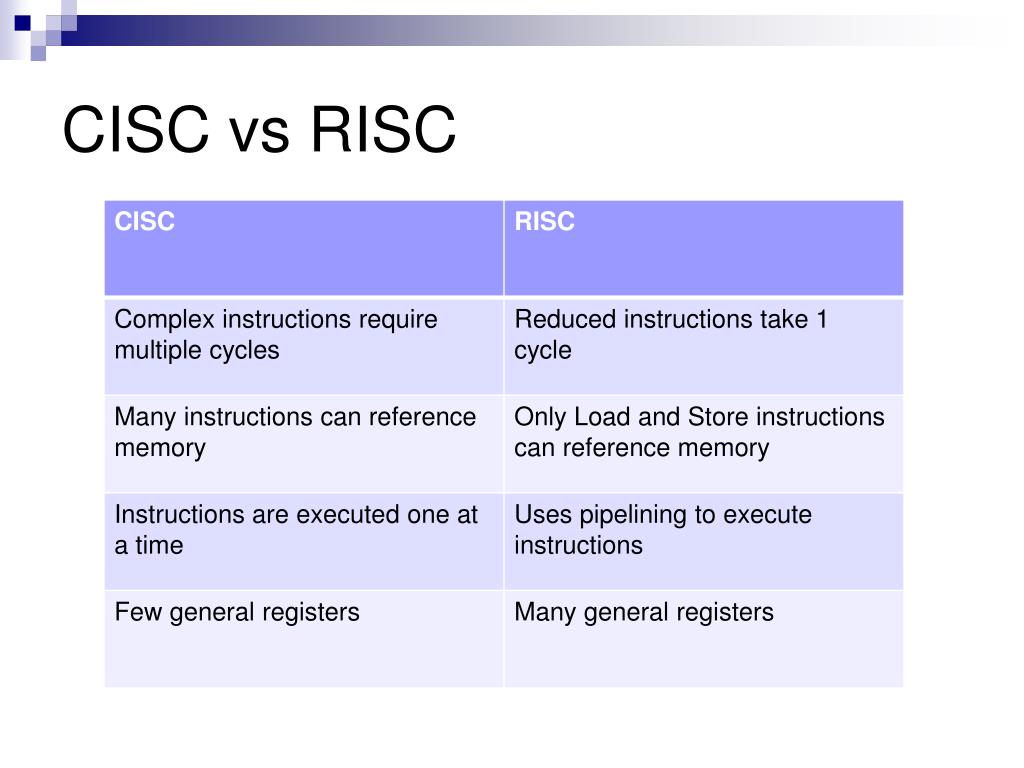

CISC и RISC: 20 ключевых сравнений

Архитектура CISC пытается повысить производительность ЦП, выполняя задачу с минимальным количеством строк ассемблерного кода, в то время как RISC опирается на стратегию сокращение времени выполнения каждой инструкции. Например, на процессоре Intel 8086 (устройство CISC) несколько операций над двумя 8-битными числами могут потребовать от 70 до 77 тактовых циклов. Напротив, микроконтроллеру PIC (устройству RISC) может потребоваться до 38 тактовых циклов. Как видно из примера, устройство RISC в 2 раза быстрее своего аналога CISC.

Поскольку устройствам CISC требуется больше времени для выполнения одной операции, архитектура не поддерживает параллельную обработку и конвейерную обработку инструкций. Напротив, в архитектуре RISC каждая инструкция выполняется за один такт, что способствует конвейеризации инструкций.

Напротив, в архитектуре RISC каждая инструкция выполняется за один такт, что способствует конвейеризации инструкций.

Вот некоторые ключевые различия между архитектурами процессоров CISC и RISC:

| Старший номер | ЦИСК | РИСК |

| 1. | CISC — это сокращенная форма для компьютера с комплексным набором инструкций. | RISC относится к компьютеру с сокращенным набором команд. |

| 2. | Архитектура CSIC обрабатывает сложные инструкции, выполнение которых требует нескольких тактов. В среднем на одну инструкцию (CPI) требуется от двух до пяти тактов. | Архитектура RISC выполняет простые, но оптимизированные инструкции за один такт. Он обрабатывает инструкции со средней скоростью 1,5 такта на инструкцию (CPI). |

| 3. | CISC фокусируется на оборудовании, таком как транзисторы, для выполнения инструкций. | RISC больше фокусируется на программном обеспечении, таком как коды или компиляторы для выполнения инструкций. |

| 4. | Реализация сложных инструкций разрешена через блоки памяти. | RISC не имеет специальной памяти и поэтому использует специализированное оборудование для выполнения инструкций. |

| 5. | УстройстваCISC устанавливаются с блоком микропрограммирования. | УстройстваRISC имеют встроенный блок программирования. |

| 6. | CISC использует множество инструкций для выполнения сложных задач. | RISC поставляется с сокращенным набором инструкций, который обычно является примитивным по своей природе. |

| 7. | Процессоры CISC обычно имеют микрокод, что позволяет управлять ЦП на основе ПЗУ. Однако современные процессоры CISC также используют аппаратные блоки для упрощения управления ЦП. | ПроцессорыRISC используют аппаратные модули для управления процессорами. |

| 8. | Процессор CISC работает с разрядностью от 16 до 64 бит для выполнения каждой инструкции. | Процессор RISC использует 32 бита для выполнения каждой инструкции. |

| 9. | Архитектура CISC использует один кэш для хранения данных и инструкций. Однако последние разработки CISC используют разделенные кэши для разделения данных и инструкций. | Архитектура RISC использует разделенные кэши, один для данных, а другой для инструкций. |

| 10. | ПроцессорыCISC используют структуру «память-память» для выполнения таких инструкций, как ADD, LOAD и даже STORE. | ПроцессорыRISC полагаются на механизм между регистрами для выполнения инструкций ADD, STORE и LOAD. |

| 11. | Архитектура CISC использует только один набор регистров. | Архитектура RISC использует несколько наборов регистров. |

| 12. | Поскольку устройства CISC работают в многотактовой среде, они поддерживают режимы адресации в диапазоне от 12 до 24. | Поскольку машины RISC работают с одним тактовым циклом, они имеют ограниченные режимы адресации. |

| 13. | ПроцессорыCISC способны более эффективно обрабатывать операторы языка программирования высокого уровня благодаря поддержке сложных режимов адресации. | Поскольку процессоры RISC поддерживают ограниченный набор режимов адресации, сложные инструкции синтезируются с помощью программных кодов. |

| 14. | CISC не поддерживает параллелизм и конвейерную обработку. Таким образом, инструкции CISC менее конвейерны. | ПроцессорыRISC поддерживают конвейерную обработку инструкций. |

| 15. | Сложность CISC встроена в микропрограммы. | Сложность RISC связана с компиляторами, которые выполняют программу. |

| 16. | ИнструкцииCISC требуют большого времени выполнения. | ИнструкцииRISC требуют меньше времени для выполнения. |

| 17. | CISC поддерживает расширение кода, аналогичное расширению макросов, при котором копия встроенных функций добавляется в каждое место, где бы они ни вызывались. Такие встроенные функции работают быстрее, чем обычные функции. | RISC не поддерживает расширение кода. |

| 18. | В архитектуре CISC задача декодирования инструкций довольно сложна. | В процессорах RISC декодирование инструкций проще, чем в CISC. |

| 19. | Некоторые примеры процессоров CISC включают процессоры Intel x86, System/360, VAX, PDP-11, семейство Motorola 68000 и AMD. | Примеры процессоров RISC включают Alpha, ARC, ARM, AVR, MIPS, PA-RISC, PIC, Power Architecture и SPARC. |

| 20. | ПроцессорыCISC используются для недорогих приложений, таких как устройства домашней автоматизации, системы безопасности и т. д. | ПроцессорыRISC подходят для высокопроизводительных приложений, включая обработку изображений и видео, телекоммуникации и т. д. |

RISC или CISC: какая архитектура лучше?

Каждая архитектура процессора по-своему мощна. В результате оба типа используются для разных приложений, как показано в сравнительной таблице выше.

Если вы посмотрите на историю этих типов процессоров, то поймете, что архитектура CISC была весьма популярна, когда микропроцессоры и микроконтроллеры только появились. Это было связано с ограниченным доступом к возможностям программного обеспечения в то время. Однако со временем область программного обеспечения стала более зрелой, и с ее растущей сложностью такие компании, как Apple, инвестировали в разработку архитектуры RISC.

Однако на сегодняшний день архитектура CISC практически устарела, поскольку ее разработка становится все более сложной. Поскольку технология была разработана Intel, компания продолжала инвестировать в нее, чтобы обеспечить обратную совместимость своего аппаратного и программного обеспечения с процессорами x86.

Современные передовые устройства ARM, микроконтроллеры PIC и интеллектуальные устройства, такие как смартфоны, используют архитектуру RISC, поскольку они энергоэффективны, требуют меньше ресурсов и работают быстрее. Единственными устройствами CISC, существующими сегодня, являются процессоры Intel серии x86.

Подробнее: Что такое телематика? Значение, работа, типы, преимущества и приложения в 2022 году

Вывод

Споры о том, какая архитектура лучше, ведутся с начала 1980-х годов. Однако, изучив оба процессора, понимаешь, что однозначного ответа на этот вопрос нет. CISC в большей степени ориентирован на аппаратное обеспечение, а это означает, что количество транзисторов на микросхемах может только увеличиваться в ближайшие годы, тем самым увеличивая сложность аппаратного обеспечения. Напротив, RISC представляет собой программно-ориентированную архитектуру, которую легче внедрять и модифицировать. В результате он может выйти на рынок за гораздо меньшее время и продолжить делать это в ближайшем будущем.

Напротив, RISC представляет собой программно-ориентированную архитектуру, которую легче внедрять и модифицировать. В результате он может выйти на рынок за гораздо меньшее время и продолжить делать это в ближайшем будущем.

Поскольку каждый подход имеет свою долю преимуществ и недостатков, трудно принять участие в дебатах о лучшей архитектуре между CISC и RISC.

Помогла ли вам эта статья понять различия между архитектурами процессоров RISC и CISC? Прокомментируйте ниже или дайте нам знать на Facebook Открывает новое окно , Twitter Открывает новое окно 900

36

LinkedIn Открывает новое окно . Мы хотели бы услышать от вас!Источник изображения: Shutterstock

БОЛЬШЕ О ТЕХНИКЕ

- Что такое Интернет всего? Значение, примеры и использование

- Что такое тактильные ощущения? Значение, типы и важность

- Что такое NFT (невзаимозаменяемый токен)? Определение, работа, использование и примеры

- Пять лучших решений для удаленного управления ПК в эпоху гибридной работы

- Что такое QoS (качество обслуживания)? Значение, работа, важность и применение

Чем отличаются процессоры RISC и CISC?

Если вы увлекаетесь технологиями, возможно, вы слышали слова «компьютер с сокращенным набором команд» (RISC) и «компьютер со сложным набором команд» (CISC). И если вы немного разбираетесь в компьютерах, вы также можете знать, что эти термины относятся к различным способам проектирования процессора.

И если вы немного разбираетесь в компьютерах, вы также можете знать, что эти термины относятся к различным способам проектирования процессора.

Например, процессор ARM в вашем телефоне имеет архитектуру RISC. Напротив, процессор x86 на вашем компьютере имеет дизайн CISC.

Но в чем разница между RISC и CISC? Давайте копнем немного глубже и узнаем.

Что такое набор инструкций?

Когда бы мы ни говорили о различных конструкциях центральных процессоров (ЦП), одной из вещей, о которых мы должны говорить, является набор инструкций.

Набор инструкций ЦП — это набор операций, которые ЦП может выполнять изначально. Это операции, которые закодированы в ЦП на аппаратном уровне. Этот набор может содержать от нескольких до тысяч инструкций, в зависимости от конструкции процессора.

Другими словами, ЦП не может выполнять никакие операции, выходящие за рамки его набора инструкций, потому что у него нет для этого оборудования.

Давайте используем аналогию, чтобы лучше понять это. Берите пример с лампочки. Производитель лампочки разработал лампочку для преобразования электричества в свет. И лампочка может сделать это, потому что аппаратное обеспечение изначально поддерживает это.

Берите пример с лампочки. Производитель лампочки разработал лампочку для преобразования электричества в свет. И лампочка может сделать это, потому что аппаратное обеспечение изначально поддерживает это.

По сути, лампочка может только преобразовывать электричество в свет и ничего больше.

Аналогично, набор инструкций ЦП — это набор операций, которые разрешает аппаратное обеспечение ЦП. Например, почти все процессоры имеют в своем наборе инструкций команду «Move». Инструкция «Переместить» берет некоторые данные из исходного пространства хранения и перемещает их в место назначения.

Всякий раз, когда процессору необходимо переместить какие-либо данные, он точно знает, как это сделать, потому что аппаратное обеспечение было разработано для этого.

Короче говоря, набор инструкций содержит все те операции, которые процессор поддерживает на аппаратном уровне.

Как работает процессор?

Процессор представляет собой лабиринт электрических цепей. Эти электрические схемы спроектированы таким образом, чтобы дать процессору собственный набор инструкций. Таким образом, он знает только, как выполнять операции в наборе инструкций, поскольку у него есть схема для этого.

Эти электрические схемы спроектированы таким образом, чтобы дать процессору собственный набор инструкций. Таким образом, он знает только, как выполнять операции в наборе инструкций, поскольку у него есть схема для этого.

Чтобы заставить ЦП выполнить определенную операцию, схема, соответствующая этой операции, запускается электрическим сигналом. И как только цепь запускается, ЦП выполняет процедуру, связанную с этой схемой.

Чтобы заставить ЦП выполнять сложные операции, такие как отправка твита, программы запускают миллионы электрических сигналов каждую секунду, каждый из которых нацелен на определенную инструкцию из набора инструкций ЦП.

Вот тут-то и появляется концепция RIS и CIS .

Что такое RISC?

Как следует из названия, RISC-процессор имеет упрощенный набор операций. Эти упрощенные инструкции достигают простых целей и занимают всего один цикл.

А поскольку в RISC есть простые инструкции, ЦП не нужно иметь сложную схему для выполнения этих инструкций. Это также объясняет, почему RISC-проекты с точки зрения аппаратного обеспечения дешевле реализовать.

Это также объясняет, почему RISC-проекты с точки зрения аппаратного обеспечения дешевле реализовать.

Связано: Почему мой телефон работает медленнее, чем компьютер? Разъяснение скоростей смартфонов и настольных компьютеров

Чтобы более подробно понять RISC-процессор, давайте рассмотрим принципы проектирования RISC-процессоров.

Во-первых, процессоры RISC выполняют каждую инструкцию за один цикл.

Во-вторых, процессоры RISC выполняют операции только с данными, хранящимися в регистрах. Это связано с тем, что одним из основных узких мест в способности ЦП выполнять задачи является огромное несоответствие между скоростью ЦП и скоростью основной памяти. Основная память очень медленная по сравнению с процессором.

Связано: Краткое и грязное руководство по оперативной памяти: что вам нужно знать

Таким образом, если ЦП должен использовать данные, хранящиеся в основной памяти, это будет узким местом устройства, и процесс будет медленным. В RISC-дизайне данные загружаются и сохраняются в регистрах ЦП, потому что скорость регистров гораздо ближе к скорости ЦП, чем основная память.

В-третьих, инструкции RISC достаточно просты, так что нет слоя интерпретирующего микрокода для преобразования инструкций в более простые формы.

И, наконец, проекты RISC поддерживают конвейерную обработку для одновременного выполнения частей нескольких инструкций. Поскольку ЦП с архитектурой RISC имеют более высокие тактовые частоты, они работают исключительно быстро. Конвейерная обработка — это способ воспользоваться этой скоростью и выполнить части нескольких инструкций для повышения эффективности.

Короче говоря, процессоры RISC имеют простые инструкции, более высокие тактовые частоты, эффективную структуру конвейерной обработки, операции загрузки-сохранения в регистрах и могут выполнять инструкции за один цикл.

Что такое CISC?

CISC является противоположностью RISC почти во всех ключевых областях. Почти все чипы для настольных ПК имеют дизайн CISC.

Во-первых, инструкции проектирования CISC сложны и поэтому требуют слоя микрокода для преобразования в симплексные инструкции.

Во-вторых, для выполнения инструкций CISC может потребоваться несколько циклов ЦП.

В-третьих, конвейерная обработка не так эффективна в CISC, и ее еще сложнее реализовать из-за сложной природы инструкций CISC.

Короче говоря, процессоры с архитектурой CISC могут выполнять множество операций в одной сложной инструкции. Но для выполнения инструкции требуется несколько циклов, ее сложнее использовать в конвейерной обработке, и она требует большого количества схем на ЦП.

RISC и CISC: ключевые отличия

Основное различие между RISC и CISC заключается в типе выполняемых ими инструкций.

Инструкции RISC просты, выполняют только одну операцию, и ЦП может выполнить их за один цикл.

9Инструкции 0002 CISC, с другой стороны, упаковываются в кучу операций. Таким образом, ЦП не может выполнить их за один цикл. Инструкции также являются причиной того, что ЦП RISC поддерживают конвейерную обработку с самого начала, а ЦП CISC с этим сложнее. В RISC инструкции достаточно просты, чтобы их можно было выполнять по частям. С CISC это сделать сложнее из-за сложного характера инструкций.

В RISC инструкции достаточно просты, чтобы их можно было выполнять по частям. С CISC это сделать сложнее из-за сложного характера инструкций.

Далее, в отличие от RISC, инструкции CISC могут работать непосредственно из ОЗУ. Таким образом, нет необходимости выполнять отдельные операции загрузки/сохранения в дизайне CISC.

Наконец, требования к оборудованию для конструкции CISC выше, чем для конструкции RISC, поскольку CISC требует, чтобы сложные инструкции были встроены в аппаратное обеспечение ЦП. По сути, то, что CISC достигает с помощью аппаратного обеспечения, RISC стремится достичь с помощью программного обеспечения.

Вот почему программы, ориентированные на архитектуру CISC, имеют меньше строк кода, поскольку сами инструкции обрабатывают множество операций.

Как у RISC, так и у CISC есть свои преимущества и недостатки

Ни один современный процессор не основан полностью ни на RISC, ни на CISC. Современные процессоры включают в себя принципы проектирования обеих архитектур, чтобы получить лучшее из обоих миров.