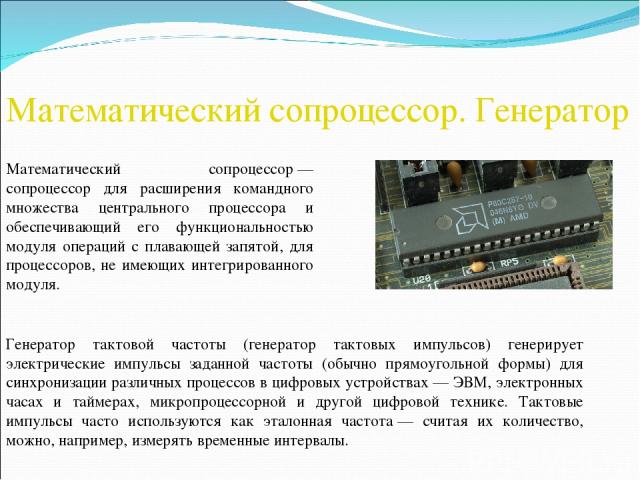

Лекция 4-1. masm64. Математический сопроцессор

Опубликовано 27.09.2018 автором asm

Ссылка

Запись опубликована в рубрике Без рубрики. Добавьте в закладки постоянную ссылку.

Чтение материалов сайта может привести к изменению Вашего мышления и вывести сознание из привычного равновесия. А это вряд ли сделает Вас счастливее, ведь знания умножают печали… «Во многой мудрости много печали; и кто умножает познания, умножает скорбь» — царь Соломон

Случайная цитата

Свежие записи

- Реверсное программирование 09.02.2022

- Системное программирование 16.10.2020

- Системное программирование 12.10.2020

Кафедра КИП НТУ ХПИ

Веб-сайт кафедры КИП (с 2022): https://web.kpi.kharkov.ua/cep/

Discord-server: https://discord.gg/kZEzDV7

Telegram канал: https://t.

me/khpi_otp

me/khpi_otpYoutube: https://www.youtube.com/@kafedra_kip

Instagram: https://www.instagram.com/_.k.i.p._/

Tik-Tok: https://vm.tiktok.com/ZMLnv3dYD/

Facebook: https://www.facebook.com/KafedraKIP/

PlayMarket: https://play.google.com/store/apps/de…

linkedIn: www.linkedin.com/company/kafedra-kip

Дирекция КН института [email protected]

Факультет КИТ (старый сайт) https://web.kpi.kharkov.ua/cit/ru

http://www.kpi.kharkov.ua/rus/faculty/kit/

Информационно-вычислительный центр http://web.kpi.kharkov.ua

НТУ ХПИ

НТУ ХПИ Сайты НТУ “ХПИ

Декабрь 2022 Пн Вт Ср Чт Пт Сб Вс 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 календарь праздников

Информер с курсом валют

Архивы

Архивы Выберите месяц Февраль 2022 (1) Октябрь 2020 (2) Июнь 2020 (2) Ноябрь 2019 (1) Октябрь 2019 (1) Май 2019 (2) Апрель 2019 (2) Ноябрь 2018 (9) Октябрь 2018 (6) Сентябрь 2018 (6) Апрель 2018 (2) Февраль 2018 (1) Декабрь 2017 (2) Ноябрь 2017 (10) Октябрь 2017 (9) Сентябрь 2017 (14) Июнь 2017 (2) Май 2017 (2) Апрель 2017 (2) Февраль 2017 (1) Январь 2017 (5) Декабрь 2016 (4) Ноябрь 2016 (8) Октябрь 2016 (5) Сентябрь 2016 (2) Май 2016 (1) Апрель 2016 (1) Февраль 2016 (1) Декабрь 2015 (3)Найти:

Метки

КИТ26В Объявление на 16.

09.2016

СП. Лекции

Фото

09.2016

СП. Лекции

Фото

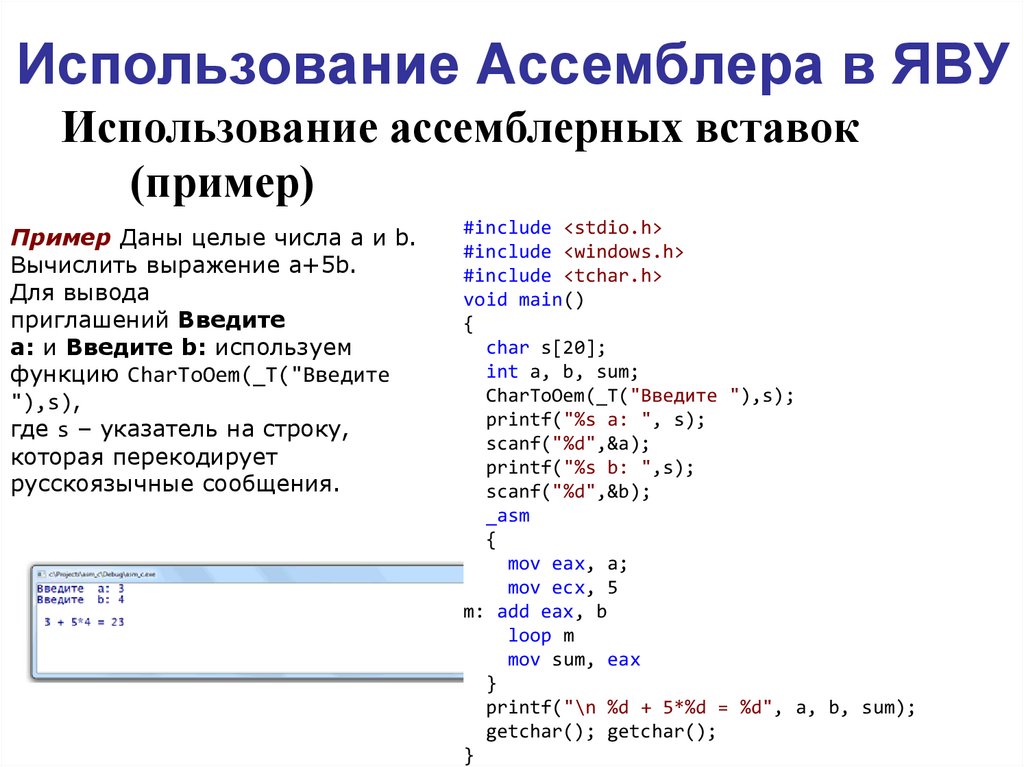

Программирование — Ассемблер сопроцессор

Пример 1: Вычислить 6 значений функции: Yn = 4x/(x + 5) (хизменяется от 3 с шагом 1,25). Результат округлить к целому, разместить в памяти и вывести на экран.

1.1 Текст программы

.386 ; директива определения типа микропроцессора

.model flat,stdcall ; задание линейной модели памяти

option casemap:none ; отличие малых и больших букв

include \masm32\include\windows.inc

include \masm32\include\kernel32.inc

include \masm32\include\fpu.inc

include \masm32\include\user32.inc

includelib \masm32\lib\user32.lib

includelib \masm32\lib\kernel32.lib

.data ; директива определения данные

_x dd 3 ; сохранение в 32-разрядном амбарчике памяти переменной х

_y dd 0 ; резервирование 32-х разрядов памяти для переменной в

tmp1 dd ? ; резервирование 32-х разрядов памяти для переменной tmp1

tmp2 dd ? ; резервирование 32-х разрядов памяти для переменной tmp2

hod dd 1. 25

25

krok dd 5

_umnoj dd 4 ; умножение на 4

probel dd 09h ; для вывода на экран

res dd 0

ifmt db «Yn = %d»,0

st1 db «Yn = 4x/(x + 5) «,0

st2 dd 10 dup(?),0

st3 dd 10 dup(?),0

.code ; директива начала кода программы

_start: ; директива начала кода программы

lea edi,st2

lea esi,st3

xor eax,eax ; обнуление регистров

xor ebx,ebx

xor ecx,ecx

xor edx,edx

finit ; инициирующее сопроцессора

fild _x

m1:

fld st(0)

fiadd krok

fld st(1)

fimul _umnoj

fmul st(0),st(1)

fistp dword ptr [edi]

fistp dword ptr [esi]

fadd hod

add edi,4

loop m1

lea edi,st2

mov eax[edi+20]

invoke wsprintf \

ADDR st2 \

ADDR ifmt \

eax

invoke MessageBox \

NULL \

addr st2 \

addr st1 \

MB_OK

invoke ExitProcess,0

end _start ; зак?нчення программы

1. 2 Результат работы программы

2 Результат работы программы

Пример 2 : Определить номер (х) элемента функции: xn = 3х + 5, при котором сумма элементов превысит 12 000. Результат разместить в памяти и вывести соответствующие сообщения.

2.1 Текст программы

.386 ; директива определения типа микропроцессора

.model flat,stdcall ; задание линейной модели памяти

option casemap:none ; отличие малых и больших букв

include \masm32\include\windows.inc

include \masm32\include\kernel32.inc

include \masm32\include\fpu.inc

include \masm32\include\user32.inc

includelib \masm32\lib\user32.lib

includelib \masm32\lib\kernel32.lib

includelib \masm32\lib\fpu.lib

.data ; директива определения данные

_x dd 0 ; сохранение переменной х

_y dd 0 ; резервирование 32-х разрядов памяти для переменной в

tmp1 dd ? ; резервирование 32-х разрядов памяти для переменной tmp1

tmp2 dd ? ; резервирование 32-х разрядов памяти для переменной tmp2

hod dd 1

krok dd 3

plus dd 5

mem dw ?

_MASK equ 0C00h

limit dd 12000

ifmt db «№ = %d»,0

st1 db «Вывод номера елемента»,0

st2 dd 10 dup(?),0

. code ; директива начала кода программы

code ; директива начала кода программы

_start: ; директива начала кода программы

lea edi,st2

lea esi,st3

xor eax,eax ; обнуление регистров

xor ebx,ebx

xor ecx,ecx

xor edx,edx

mov edx,limit

finit ; инициализация сопроцессора

fstcw mem

OR mem,_MASK

fldcw mem

mov ecx,6

m1:

inc _x

fild _x

fild krok

fyl2x

fld st(0)

frndint

fsub st(1),st(0)

frndint

f2xm1

fiadd hod

fldz

fadd st(0),st(2)

f2xm1

fiadd hod

fmul st(0),st(1)

fiadd plus

fistp dword ptr [edi]

fistp dword ptr [esi]

fistp dword ptr [esi]

mov eax[edi]

add ebx,eax

add edi,4

add esi,4

cmp edx,ebx

jns m1

mov eax,_x

invoke wsprintf \

ADDR st2 \

eax

invoke MessageBox \

NULL \

addr st2 \

addr st1 \

MB_OK

invoke ExitProcess,0

end _start ; зак?нчення программы

2. 2 Результат работы программы

2 Результат работы программы

Пример 3: Вычислить 4 значения функции: Y = 3 * log2(x2+1), x изменяется от 0,2 с шагом 0,3.

3.1 Текст программы

.386 ; директива определения типа микропроцессора

.model flat,stdcall ; задание линейной модели памяти

option casemap:none ; отличие малых и больших букв

include \masm32\include\windows.inc

include \masm32\include\kernel32.inc

include \masm32\include\fpu.inc

include \masm32\include\user32.inc

includelib \masm32\lib\user32.lib

includelib \masm32\lib\kernel32.lib

includelib \masm32\lib\fpu.lib

.data ; директива определения данные

_x dd 0.2 ; сохранение в 32-разрядном амбарчике памяти переменной х

_y dd 0 ; резервирование 32-х разрядов памяти для переменной в

tmp1 dd ? ; резервирование 32-х разрядов памяти для переменной tmp1

tmp2 dd ? ; резервирование 32-х разрядов памяти для переменной tmp2

hod dd 0. 3

3

umnoj dd 3

const dd 4

mem dw ?

_MASK equ 0C00h

ifmt db «Y = %d»,0

st1 db «Вывод функции»,0

st2 dd 10 dup(?),0

st3 dd 10 dup(?),0

.code ; директива начала кода программы

_start: ; директива начала кода программы

lea edi,st2

lea esi,st3

xor eax,eax ; обнуление регистров

xor ebx,ebx

xor ecx,ecx

xor edx,edx

finit ; инициализания сопроцессора

OR mem,_MASK

fldcw mem

mov ecx,4

fld _x

fld _x

m1:

fild umnoj

fld st(1)

fmulp st(2),st(0)

fyl2x

fld hod

fadd st(2),st(0)

fistp dword ptr [edi]

dec const

jz m2

fistp dword ptr [esi]

fld st(0)

mov eax[esi]

add edi,4

add esi,4

loop m1

m2:

invoke FpuFLtoA, 0, 10, ADDR st2, SRC1_FPU or SRC2_DIMM

invoke MessageBox, NULL, addr st2, addr st1, MB_OK

invoke ExitProcess, NULL ; возвращение управления ОС Windows

; но освобождение ресурсов

end _start ; директива окончания программы с именем start

3. 2 Результат работы программы

2 Результат работы программы

Сопроцессор Mips 0 :: Операционные системы 2018

Процессор MIPS состоит из целочисленного процессора (ЦП) и совокупность сопроцессоров, которые выполняют вспомогательные задачи или работают на других типы данных, такие как числа с плавающей запятой.

Целочисленные арифметические и логические операции выполняются непосредственно ЦП. Операции с плавающей запятой выполняются сопроцессором 1. Используется сопроцессор 0 управлять исключениями и прерываниями.

Обычный код уровня пользователя не имеет доступа к сопроцессору 0, но прерывание и код, поддерживающий исключение, должен использовать его. Сопроцессор 0 имеет несколько регистров, которые управляет исключениями и прерываниями.

Регистр состояния сопроцесса 0 — это регистр чтения-записи, используемый для включения или отключения различных типов прерываний.

Разрешение прерывания

Если бит разрешения прерывания равен 1, прерывания разрешены. Если он равен 0, они отключены.

Если он равен 0, они отключены.

Уровень исключения

Бит уровня исключения обычно равен 0, но после исключения устанавливается в 1 имеет место. Когда этот бит равен 1, прерывания отключены и EPC не обновляется. если произойдет другое исключение. Этот бит препятствует тому, чтобы обработчик исключений был нарушено прерыванием или исключением, но его следует сбросить, когда обработчик заканчивается.

Режим пользователя

Бит режима пользователя равен 0, если процессор работает в режиме ядра, и 1, если он работает в пользовательском режиме.

Пользовательский режим установлен на 1 в Mars и Spim

Ни Mars, ни Spim не реализуют режим ядра и фиксируют бит пользовательского режима на 1.

Маска прерывания

6 прерываний аппаратного уровня и 2

прерывания на программном уровне. Бит маски, установленный в 1, разрешает прерывания на этом уровне.

прервать работу процессора. Бит маски, установленный в 0, отключает прерывания в этот момент. уровень.

уровень.

| Уровень аппаратного прерывания | Используется для | Марс | Спим | ||

|---|---|---|---|---|---|

| Номер бита. | Битовая маска | Номер бита. | Битовая маска | ||

| 0 | Передатчик (терминальный выход) | 9 | 0x00000200 | 10 | 0x00000400 |

| 1 | Приемник (прерывание клавиатуры) | 8 | 0x00000100 | 11 | 0x00000800 |

| 5 | Таймер | Не поддерживается | 15 | 0x00008000 | |

Начальное значение

При запуске регистр состояния имеет следующее значение.

| Регистр | МАРС | СПИМ |

|---|---|---|

| Состояние | 0x0000ff11 | 0x3000ff10 |

Чтобы увидеть, какие биты установлены в регистре состояния при запуске, мы должны преобразовать шестнадцатеричное значение запуска в двоичное.

Из шестнадцатеричной в двоичную

При переводе из шестнадцатеричной в двоичную мы делаем это, переводя каждую шестнадцатеричную цифру в четырехбитное двоичное значение.

-

0x0= [двоичный] =0000 -

0x1= [двоичный] =0001 -

0xf= [двоичный] =1111

Затем мы заменяем каждую шестнадцатеричную цифру соответствующей четырехбитной двоичной. количество.

Mars инициализирует регистр состояния в сопроцессоре от 0 до 0x0000ff11 = [двоичный] = 0000 0000 0000 0000 1111 1111 0001

0001 .

При запуске:

- Прерывания разрешены.

- Пользовательский режим установлен на 1.

- Все биты маски прерывания установлены в 1.

Причина (регистр 13)

Регистр причины в основном доступен только для чтения, значение которого устанавливается

системы при возникновении прерывания или исключения. В нем указывается, какой

только что произошло прерывание или исключение.

В нем указывается, какой

только что произошло прерывание или исключение.

При возникновении исключения или прерывания код сохраняется в регистре причины как 5-битное значение (биты 2-6). Это поле обычно называют исключением код, хотя он используется как для исключений, так и для прерываний.

| Код исключения | Имя | Причина исключения |

|---|---|---|

| 0 | Интервал | Прерывание (аппаратное) |

| 4 | АдЭЛ | Ошибка адреса (загрузка или выборка инструкций) |

| 5 | АдЕС | Исключение ошибки адреса (сохранение) |

| 6 | МБП | Ошибка шины выборки инструкций |

| 7 | ДБЕ | Загрузка или сохранение данных Ошибка шины |

| 8 | Сис | Исключение системного вызова |

| 9 | Бп | Исключение точки останова |

| 10 | РИ | Исключение обратной инструкции |

| 11 | ЦП | Сопроцессор Не реализован |

| 12 | Ов | Исключение арифметического переполнения |

| 13 | Тр | Ловушка |

| 14 | ФПО | Исключение с плавающей запятой |

EPC (регистр 14)

Регистр счетчика исключительных программ (EPC). При возникновении прерывания или исключения

адрес выполняемой в данный момент инструкции копируется из программы

Счетчик (ПК) к EPC. Это адрес, на который возвращается ваш обработчик, когда он

заканчивается.

При возникновении прерывания или исключения

адрес выполняемой в данный момент инструкции копируется из программы

Счетчик (ПК) к EPC. Это адрес, на который возвращается ваш обработчик, когда он

заканчивается.

Таймер (регистры 9 и 11)

В SPIM таймер имитируется двумя дополнительными регистрами сопроцессора: Счетчик (регистр 9), значение которого аппаратно постоянно увеличивается, и Сравните (регистр 11), значение которого можно установить. Когда считать и сравнивать равны, прерывание вызывается в регистре причины, бит 15.

Чтобы запланировать прерывание по таймеру, используется хранится в регистре сравнения. Чем меньше временной интервал, тем больше частота прерываний таймера.

В Mars нет таймера

Прерывания по таймеру еще не реализованы в MARS.

Доступ к регистрам в сопроцессоре 0

Для доступа к регистру в сопроцессоре значение регистра должно быть передано из

Сопроцессор 0 в один из обычных регистров ЦП. Чтобы обновить один из

регистрирует в сопроцессоре 0 значение в одном из обычных регистров ЦП в

ЦП должен быть переведен в один из регистров сопроцессора 0.

Чтобы обновить один из

регистрирует в сопроцессоре 0 значение в одном из обычных регистров ЦП в

ЦП должен быть переведен в один из регистров сопроцессора 0.

Если вы хотите изменить значение в регистре сопроцессора 0, вам нужно переместить

значение регистра в регистр общего назначения с mfc0 , измените значение

туда и верните измененное значение с помощью mtc0 .

mfc0

Команда mfc0 (переместить из сопроцессора 0) перемещает значение из регистра сопроцессора 0 в регистр общего назначения.

Пример:

mfc0 $t5, $13 # Копировать $13 (причина) из сопроцессора 0 в $t5.

mtc0

Команда mtc0 (переместить в сопроцессор 0) перемещает значение из

регистр общего назначения в регистр сопроцессора 0.

Пример:

mtc0 $v0, $12 # Копировать $v0 в $12 (статус) в сопроцессоре 0.

Ссылки

Ассемблеры, компоновщики и симулятор SPIM

Настройка процессора через сопроцессор 15

Настройка процессора через сопроцессор 15

Введение

Процессоры ARM после (и включая) ARM 3 предлагают различные идентификаторы и внутреннюю конфигурацию. средства путем предоставления внутреннего сопроцессора 15, из которого вы можете считывать и записывать.

средства путем предоставления внутреннего сопроцессора 15, из которого вы можете считывать и записывать.Настройка управляется регистрами сопроцессора 15, доступ к которым осуществляется с помощью MRC и MCR в непользовательском режиме.

Эти регистры специфичны для указанного процессора.

АРМ 3

- Регистр 0– Идентификация процессора (только чтение)

Биты 0–7 Версия процессора Биты 8–15 должны быть равны «3», идентифицируя процессор как ARM3. Биты 16–23 Код производителя (&56 = VLSI Technology Inc.) Биты 24–31 Код конструктора (&41 = ARM Ltd)

- Регистр 1 — Очистка кэша (только запись)

Зависит от записи, запись чего-либо в регистр 1 приведет к очистке кэша.

- Регистр 2 — Разное управление

Бит 0 — включает (1) или выключает кэш (0) Бит 1 — определяет, используется ли в пользовательском и непользовательском режимах один и тот же адрес.

отображение. 1, если да, или 0. Должно быть 1 для использования с MEMC.

Бит 2 - 0 для нормальной работы, 1 для специального режима монитора (процессор

работает со скоростью памяти, а адрес/данные всегда помещаются на внешний

контакты, даже если данные получены из кеша - для логического анализатора

для правильной трассировки программы).

Остальные биты зарезервированы.

отображение. 1, если да, или 0. Должно быть 1 для использования с MEMC.

Бит 2 - 0 для нормальной работы, 1 для специального режима монитора (процессор

работает со скоростью памяти, а адрес/данные всегда помещаются на внешний

контакты, даже если данные получены из кеша - для логического анализатора

для правильной трассировки программы).

Остальные биты зарезервированы.

- Регистр 3 — Кэшируемые области

Управляет кэшируемыми областями памяти фрагментами по 2 МБ.Бит 0–1, если виртуальные адреса &0000000-&01FFFFF кэшируются, 0, если нет Бит 0–1, если виртуальные адреса &0200000-&03FFFFF кэшируются, 0, если нет ... Бит 31 — 1, если виртуальные адреса &3E00000-&3FFFFFF кэшируются, 0, если нет

- Регистр 4 — Какие области могут быть обновлены

Определяет, какие области памяти могут обновляться фрагментами по 2 Мб. пишет в необновляемый память идет в реальную память, а не в кеш. Это подходит для таких вещей, как ПЗУ, поскольку

вы не хотите, чтобы кэшированные данные изменялись при попытках записи.

Это подходит для таких вещей, как ПЗУ, поскольку

вы не хотите, чтобы кэшированные данные изменялись при попытках записи.Бит 0–1, если виртуальные адреса &0000000-&01FFFFF могут быть обновлены, 0, если нет Бит 0–1, если виртуальные адреса &0200000-&03FFFFF могут быть обновлены, 0, если нет ... Бит 31 — 1, если виртуальные адреса &3E00000-&3FFFFFF могут быть обновлены, 0, если нет

- Регистр 5 — Какие области памяти являются разрушительными

Управляет тем, какие области памяти являются разрушительными, фрагментами по 2 МБ. Пишет в деструктивные области памяти приводят к очистке кеша. Например, запись в физическую память по адресу &2000000-&2FFFFFF в системе MEMC обычно кэширует виртуальные адреса памяти. и если это место было закэшировано, попытка прочитать его приведет к считыванию старого содержимого.Бит 0–1, если виртуальные адреса &0000000-&01FFFFF являются разрушительными, 0, если нет Бит 0–1, если виртуальные адреса &0200000-&03FFFFF являются разрушительными, 0, если нет .

..

Бит 31 — 1, если виртуальные адреса &3E00000-&3FFFFFF являются разрушительными, 0, если нет

..

Бит 31 — 1, если виртуальные адреса &3E00000-&3FFFFFF являются разрушительными, 0, если нет

АРМ 610

- Регистр 0 — Идентификация процессора (только чтение)

Возвращаемое значение для процессора ARM610 должно быть &4156061x.Биты 0–7 Версия процессора (&1x) Биты 8–15 Идентификатор процессора Биты 16–23 Код производителя (&56 = VLSI Technology Inc.) Биты 24–31 Код конструктора (&41 = ARM Ltd)

- Регистр 1 — Управление (только запись)

Все значения устанавливаются на 0 при включении питания.Бит 0 — Встроенный MMU выключен (0) или включен (1) Бит 1 — Ошибка выравнивания адресов отключена (0) или включена (1) Бит 2 — Кэш инструкций/данных выключен (0) или включен (1) Бит 3 — буфер записи выключен (0) или включен (1) Бит 4 - 26-битное пространство программы, если 0, 32-битное пространство программы, если 1 Бит 5 - 26-битное пространство данных, если 0, 32-битное пространство данных, если 1 Бит 6 — режим раннего прерывания, если 0, режим позднего прерывания, если 1 Бит 7 — операция с прямым порядком байтов, если 0, с прямым порядком байтов, если 1 Бит 8 — системный бит — управляет системой разрешений ARM610.

- Регистр 2 — База таблицы перевода (только запись)

Биты 14–31 содержат базу текущей активной таблицы страниц первого уровня.

- Регистр 3 — Управление доступом к домену (только запись)

В этом регистре хранится текущий контроль доступа для доменов с 0 по 15. В каждом домене есть два биты (домен 0 бит 0,1 … домен 15 бит 30,31), которые могут быть установлены следующим образом:00 Нет доступа — ошибка домена возникает при попытке доступа 01 Клиент — доступы проверяются на соответствие битам разрешения в дескриптор раздела/страницы 10 Зарезервировано — в настоящее время ведет себя как режим отсутствия доступа. 11 Менеджер - Доступы НЕ проверяются, ошибки разрешений не могут быть сгенерирован

- Регистр 4 — Зарезервировано — не пытаться получить доступ

- Регистр 5 — Состояние ошибки страницы/сброс TLB

При чтении сохраняется состояние последней ошибки данных (не обновляется для предварительной выборки). вина). Только младший байт имеет значение.

вина). Только младший байт имеет значение.Биты 0–3 Статус Биты 4–7 Домен Биты 8–11 установлены в ноль Биты 12 - 31 Каким бы ни было последнее значение на внутренней шине данных

При записи в этот регистр любое записанное значение вызовет блокировку трансляции. Буфер для промывки.

- Регистр 6 — Адрес сбоя данных / очистка TLB

При чтении этого регистра можно определить виртуальный адрес сбоя последней страницы.

При записи в этот регистр заданное значение (в битах 14–31) рассматривается как адрес. TLB будет искать соответствующий адрес, и если он будет найден, он будет помечен как инвалид. Это позволяет обновлять таблицу страниц в основной памяти и теперь недействительные записи во встроенном TLB должны быть очищены без штрафа за сброс весь ТЛБ.

- Регистр 7 — Сброс IDC (только запись)

Любые данные, записанные в это место, вызовут сброс IDC (кэш инструкций/данных). покраснел.

покраснел.

- Регистры с 8 по 15 — Зарезервировано

Доступ к этим регистрам приведет к срабатыванию ловушки неопределенных инструкций.

АРМ 710

Это похоже на ARM610.- Регистр 0 — Идентификатор процессора (только чтение)

Возвращаемое значение для процессора ARM610 должно быть &4104710x.Биты 0–3 Версия процессора? Биты 3–15 Идентификатор процессора — &710 Биты 16–23 Код производителя Биты 24–31 Код конструктора (&41 = ARM Ltd)

- Регистр 1 — Управление (только запись)

Все значения устанавливаются на 0 при включении питания.Бит 0 — Встроенный MMU выключен (0) или включен (1) Бит 1 — Ошибка выравнивания адресов отключена (0) или включена (1) Бит 2 — Кэш инструкций/данных выключен (0) или включен (1) Бит 3 — буфер записи выключен (0) или включен (1) Бит 4 - 26-битное пространство программы, если 0, 32-битное пространство программы, если 1 Бит 5 - 26-битное пространство данных, если 0, 32-битное пространство данных, если 1 Бит 6 — режим раннего прерывания, если 0, режим позднего прерывания, если 1 Бит 7 — операция с прямым порядком байтов, если 0, с прямым порядком байтов, если 1 Бит 8 — системный бит — управляет системой разрешений ARM710.

Бит 9- ROM bit - управляет системой разрешений ARM710

Бит 9- ROM bit - управляет системой разрешений ARM710

- Регистр 2 — База таблицы перевода (только запись)

Биты 14–31 содержат базу текущей активной таблицы страниц первого уровня.

- Регистр 3 — Управление доступом к домену (только запись)

В этом регистре хранится текущий контроль доступа для доменов с 0 по 15. В каждом домене есть два биты (домен 0 бит 0,1 … домен 15 бит 30,31), которые могут быть установлены следующим образом:00 Нет доступа — ошибка домена генерируется при попытке доступа 01 Клиент — доступы проверяются на соответствие битам разрешения в дескриптор раздела/страницы 10 Зарезервировано — в настоящее время ведет себя как режим отсутствия доступа. 11 Менеджер - Доступы НЕ проверяются, ошибки разрешений не могут быть сгенерирован

- Регистр 4 — Зарезервировано — не пытаться получить доступ

- Регистр 5 — Состояние ошибки страницы / сброс TLB

При чтении сохраняется состояние последней ошибки данных (не обновляется для предварительной выборки). вина). Только младший байт имеет значение.

вина). Только младший байт имеет значение.Биты 0–3 Статус Биты 4–7 Домен Биты 8–11 установлены в ноль Биты 12 - 31 Каким бы ни было последнее значение на внутренней шине данных

При записи в этот регистр любое записанное значение вызовет блокировку трансляции. Буфер для промывки.

- Регистр 6 — Адрес ошибки данных / очистка TLB

При чтении этого регистра можно определить виртуальный адрес последней страницы отказа.

При записи в этот регистр заданное значение (в битах 14–31) рассматривается как адрес. TLB будет искать соответствующий адрес, и если он будет найден, он будет помечен как инвалид. Это позволяет обновлять таблицу страниц в основной памяти и теперь недействительные записи во встроенном TLB должны быть очищены без штрафа за сброс весь ТЛБ.

- Регистр 7 — Сброс IDC (только запись)

Любые данные, записанные в это место, вызовут сброс IDC (кэш инструкций/данных). покраснел.

покраснел.

- Регистры с 8 по 15 — Зарезервировано

Доступ к этим регистрам приведет к срабатыванию ловушки неопределенных инструкций.

АРМ 7500

Регистры точно такие же, как у ARM710, за исключением идентификатора процессора (регистр 0). другой. В техническом описании не указано, чего следует ожидать.

РУКА 7500FE

Регистры точно такие же, как у ARM710, за исключением идентификатора процессора (регистр 0). другой. В техническом описании не указано, чего следует ожидать, однако опрос Телевизионная приставка Bush показывает и 41077100 .

StrongARM SA110

- Регистр 0 — Идентификация процессора (только чтение)

Возвращаемое значение для процессора SA110 должно быть &4401A10x.Биты 0–3 Номер версии процессора

- Регистр 1 — Управление (чтение/запись)

Все значения установлены на 0 при включении питания.

Бит 0 — Встроенный MMU выключен (0) или включен (1) Бит 1 — Ошибка выравнивания адресов отключена (0) или включена (1) Бит 2 — кеш данных выключен (0) или включен (1) Бит 3 — буфер записи выключен (0) или включен (1) Бит 7 — операция с прямым порядком байтов, если 0, с прямым порядком байтов, если 1 Бит 8 — системный бит — управляет системой разрешений MMU Бит 9- ROM bit - управляет системой разрешений MMU Бит 12 — кэш инструкций выключен (0) или включен (1)

- Регистр 2 — База таблицы преобразования (чтение/запись)

Биты 14–31 содержат базу текущей активной таблицы страниц первого уровня.

- Регистр 3 — Управление доступом к домену (чтение/запись)

В этом регистре хранится текущий контроль доступа для доменов с 0 по 15.

Документ, который у меня есть, не содержит дополнительных подробностей, хотя я полагаю, что он аналогичен к использованию ARM610/710/и т.д.

- Регистр 4 — Зарезервировано — не пытаться получить доступ

- Регистр 5 — Состояние ошибки (чтение/запись)

При чтении сохраняется состояние последней ошибки данных (не обновляется для предварительной выборки). вина). Только младший байт имеет значение.

вина). Только младший байт имеет значение.Биты 0–3 Статус Биты 4–7 Домен Бит 8 ноль Биты 9–31 Не определены при чтении, игнорируются при записи

- Регистр 6– Адрес ошибки (чтение/запись)

При чтении этого регистра можно определить виртуальный адрес последней страницы ошибки.

- Регистр 7 — Управление кэшем (только запись)

Любые данные, записанные в это место, приведут к очистке выбранного кэша.Поля сопроцессора OPC_2 и CRm выбирают, какой кэш должна произойти операция: Функция OPC_2 CRm Данные Смыв I + D %0000 %0111 - Сброс I %0000 %0101 - Смыв D %0000 %0110 - Flush D single %0001 %0110 Виртуальный адрес Чистая запись D %0001 %1010 Виртуальный адрес Слив написать баф. %0100 %1010 -

- Регистр 8 — Операции TLB (только запись)

Любые данные, записанные в это место, вызовут выбранную операцию сброса TLB.

Поля сопроцессора OPC_2 и CRm выбирают, какой кэш должна произойти операция: Функция OPC_2 CRm Данные Смыв I + D %0000 %0111 - Сброс I %0000 %0101 - Смыв D %0000 %0110 - Flush D single %0001 %0110 Виртуальный адрес

- Регистры с 9 по 14 — Зарезервировано

Доступ к этим регистрам приведет к срабатыванию ловушки неопределенных инструкций.

- Регистр 15 — Проверка, часы и бездействие (только запись)

Поля сопроцессора OPC_2 и CRm выбирают следующее... Функция OPC_2 CRm Включить нечетное слово %0001 %0001 погрузка Икеш ЛФСР Включить четное слово %0001 %0010 погрузка Икеш ЛФСР Очистить Icache %0001 %0100 ЛФСР Переместить LFSR в %0001 %1000 R14, Прервать Включить часы %0010 %0001 переключение Отключить часы %0010 %0010 переключение Отключить nMCLK %0010 %0100 выход Подождите %0010 %1000 прерывать

ARM9.

..XScale К сожалению, у меня нет подробностей этих регистров.

..XScale К сожалению, у меня нет подробностей этих регистров. Попробуйте http://www.arm.com/.

Как читать эти регистры

Код, который я придумал для идентификатора процессора Bush Box, был таким: 10 DIM-код% 32

20 П% = код%

30 [ ОПЦИЯ 3

40 SWI "OS_EnterOS"

50 МРЦ CP15, 0, R0, C0, C0

60 ТСТП ПК, #&F0000000

70 МОВ R0, R0

80 МОВ ПК, R14

90 ]

100 ПЕЧАТЬ ~USR(код%) При запуске это напечатает: > БЕГ

00008FAC ОПЦИЯ 3

00008FAC EF000016 SWI "OS_EnterOS"

00008FB0 EE100F10 MRC CP15, 0, R0, C0, C0

00008FB4 E31FF20F TSTP ПК, #&F0000000

00008FB8 E1A00000 ДВИГАТЕЛЬ R0, R0

00008FBC E1A0F00E ДВИГАТЕЛЬ ПК, R14

41077100

> Обратите внимание, что этот код должен работать в привилегированном режиме.

Сопроцессоры

Существует от нуля до трех возможных сопроцессоров. Большинство настольных систем ARM не имеют логика для внешних сопроцессоров, поэтому мы можем либо использовать то, что встроено в саму ARM, или эмулируемый сопроцессор.

CP15 зарезервирован на процессорах ARM 3 и более поздних версиях для внутренней конфигурации, как описано в этот документ.

CP0 и CP1 используются системой с плавающей запятой. Это может быть либо внешняя плавающая точка чип (как в ARM 3), аппаратное обеспечение, встроенное в процессор (как в ARM 7500FE), или полностью программная эмуляция (как и в случае с FPEmulator , который мы все знаем).

Вот небольшое упражнение для вас:

10 DIM-код% 16

20 П% = код%

30 [ ОПЦИЯ 3

40 CDP CP1, 0, C0, C1, C2, 0

50 АДФС F0, F1, F3

60 МОВ ПК, R14

70 ]

>БЕГ

00008F78 ОПЦИЯ 3

00008F78 EE010102 CDP CP1, 0, C0, C1, C2

00008F7C EE010102 АДФС F0, F1, F2

00008F80 E1A0F00E ДВИГАТЕЛЬ ПК, R14

> Что ты заметил? 🙂

Когда ARM выполняет инструкцию сопроцессора или неопределенную инструкцию, она предложит ее

к любым сопроцессорам, которые могут быть подключены в настоящее время. Если оборудование доступно для обработки

дана инструкция, то ожидается, что она это сделает. Если он занят во время инструкции

предлагается, ARM будет ждать его.

Если он занят во время инструкции

предлагается, ARM будет ждать его.

Если нет сопроцессора, способного выполнить инструкцию, ARM возьмет на себя

ловушка неопределенной инструкции, и в этом случае произойдет следующее:

- PSR и ПК сохраняются (метод отличается для 26-битных и 32-битных ARM)

- Введен режим SVC (26 бит)/режим UND (32 бит), и установлен бит I PSR

- Выполняется инструкция по адресу &00000004

Чтобы вернуться, просто вытяните сохраненные ПК и PSR (зависит от 26/32 бит) и нажмите их на текущий

ПК и PSR, вроде MOVS PC, R14 в 26-битных системах. Это поднимется с

инструкции, следующей за той, которая вызвала ловушку.

Все инструкции сопроцессора могут выполняться условно. Обратите внимание, что

условные обозначения относятся к состоянию процессора ARM, а не к состоянию какого-либо из

сопроцессоры. Это связано с тем, что ARM всегда сначала пытается выполнить инструкцию и предлагает ее по очереди.

и, возможно, принимает ловушку неопределенного приложения, поэтому условия связаны с ARM.

Это связано с тем, что ARM всегда сначала пытается выполнить инструкцию и предлагает ее по очереди.

и, возможно, принимает ловушку неопределенного приложения, поэтому условия связаны с ARM.

Чтобы было понятнее:

10 DIM-код% 32

20 П% = код%

30 [ ОПЦИЯ 3

40 FLTS F0, R0

50 FLTS F1, R1

60 ФМЛС Ф2, Ф0, Ф1

70 ФИКС R0, F2

80 МОВС ПК, R14

90 ]

100 INPUT "Первое число: "A%

110 ВВОД "Вторая цифра: "B%

120 ПЕЧАТЬ USR(код%)

Это, вероятно, не будет собрано без расширенного ассемблера BASIC. В любом случае, вы можете подумать, что ARM передаст сопроцессору с плавающей запятой выполнение четырех операций.

Инструкции FP, а затем сдать обратно.

Если бы вы это сделали, вы были бы неправы!

На самом деле выполняется:

МКР CP1, 0, R0, C0, C0 МКР CP1, 0, R1, C1, C0 CDP CP1, 9, C2, C0, C1 МРЦ CP1, 0, R0, C0, C2

Стоит отметить, что objasm указывает регистры сопроцессора с помощью CR

нотация (т. е.

е. CR0 - CR15 ), которая сначала определяется директивой CN. Это не

выглядят так, как будто инструкции сопроцессора по умолчанию определены в ASM Ника Робертса, хотя я только

посмотрел в инструкции раздел «определенные символы»…

ExtBASICasm Даррена Солта предоставляет имена регистров C0 - C15 для ссылки на

сопроцессоры. Поэтому, если какой-либо из этих примеров не удается собрать, проверьте, что

format ваш ассемблер предоставляет эти инструкции.

МРК

Инструкция MRC переводит регистр сопроцессора в регистр ARM. Занимает

форма:MRCСопроцессор обозначается в большинстве ассемблеров как, , , , ,

CPx . Регистр

записывается в с использованием

операция . Это может быть, возможно, дополнительно изменено путем и . Для представления о временах

когда это может быть необходимо, рассмотрите инструкции вида

Для представления о временах

когда это может быть необходимо, рассмотрите инструкции вида LDR Ra, [Rb], #x . Конечная

может быть опущена, как в примере, но остальные части

инструкции MRC должны быть предоставлены.

MCR

Инструкция MCR передает регистр ARM в регистр сопроцессора. Занимает

форма:MCRСопроцессор может интерпретировать поля по своему усмотрению, но стандартная интерпретация заключается в том, что содержимое регистра ARM записывается в регистр сопроцессора с использованием данный код операции, который может быть дополнительно изменен вторым регистром сопроцессора и/или второй код операции., , , , ,

LDC и STC

Инструкция LDC загружает данные из памяти в регистр сопроцессора, при этом STC сохраняет данные из регистра сопроцессора в память. ARM должен предоставить адрес, сопроцессор принимает данные и контролирует, сколько перенесено.

LDCЕсли указан флаг ‘L’, выполняется длинная передача. В противном случае короткая передача выполненный. Флаг «L» следует за расширением, например, , LDCL <совладелец>, <регистрация совладельца>, <адрес> STC <совладелец>, <рег. совладельца>, <адрес> STCL <со-про>, <со-про рег>, <адрес>

LDCEQL . Адрес — это выражение, в результате которого генерируется адрес, поэтому примеры находятся:

[прием] [Rx, #x] ! [Rx], #xОни подобны тем, которые используются для инструкции LDR. Однако они только восемь битов и определяют смещения слов (типы ARM имеют 12-битное и байтовое смещение).

Происходит следующее: 8-битное беззнаковое смещение сдвигается влево на два бита и добавляется или вычитается из базовый регистр, это может быть сделано до или после использования базы в качестве адреса передачи. Новое базовое значение можно записать обратно или оставить без изменений.

Следующее отличие состоит в том, что постиндексная адресация требует явной установки бита W инструкция (в отличие от LDR/STR, которые всегда делают это при постиндексации).

Вы устанавливаете бит «W» с помощью «!» флаг, как

Вы устанавливаете бит «W» с помощью «!» флаг, как STR CP0, CR1, [R2, #16]! . Базовый регистр используется для первой передачи. Если есть дальнейшие переводы, база будет увеличиваться на одно слово для каждой из этих дополнительных передач.

CDP

Инструкция CDP предписывает сопроцессору выполнить некоторую обработку. Это занимает

форма:CDPЭто говорит сопроцессору что-то сделать. ARM не будет ждать, пока он завершится. своего рода статус, отправленный обратно в ARM. Сопроцессор может поддерживать очередь инструкции, что позволяет ему и ARM обрабатывать параллельно., , , ,

Вариант этого можно получить с аппаратным обеспечением с плавающей запятой; пока это не так (на мой знания) поддерживают очередь инструкций, это правда, что ARM будет ждать завершения FPU операцию перед предоставлением следующей. Таким образом, при тщательном кодировании можно было бы заставить ARM выполнить какую-то обработку (несколько инструкций) между отправкой инструкции в FPU и чтение его результата обратно.

me/khpi_otp

me/khpi_otp